## STUDY OF ALTERNATIVE LOGIC STYLES SUITABLE FOR LOW POWER VLSI DESIGN

A Thesis Submitted

In Partial Fulfilment of the Requirements

for the Degree of

#### **DOCTOR OF PHILOSOPHY**

in

**Department of Electronics & Communication Engineering**

by

Neetika Yadav (2K18/PhD/EC/514)

**Under the Supervision of**

Prof. Neeta Pandey (Professor, DTU, Delhi)

**Dr. Deva Nand** (Assistant Professor, DTU, Delhi)

Department of Electronics & Communication Engineering,

### **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-110042, India

November, 2024

### **CERTIFICATE**

This is to certify that the thesis entitled "STUDY OF ALTERNATIVE LOGIC STYLES SUITABLE FOR LOW POWER VLSI DESIGN" submitted by Neetika Yadav (2K18/PhD/EC/514) to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi, for the award of the degree of Doctor of Philosophy is based on the original research work carried out by her under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirement of the regulations relating to the degree. It is further certified that the work presented in this thesis is not submitted to any other university or institution for the award of any other degree or diploma.

Neela

Prof. Neeta Pandey

Supervisor

Department of Electronics &

Communication Engineering,

Delhi Technological University,

Delhi –110042

0330-A

Dr. Deva Nand

Co-Supervisor

Department of Electronics &

Communication Engineering,

Delhi Technological University,

Delhi –110042

**DECLARATION**

I hereby declare that the work presented in this thesis entitled "STUDY OF

ALTERNATIVE LOGIC STYLES SUITABLE FOR LOW POWER VLSI DESIGN"

has been carried out by me under the supervision of Prof. Neeta Pandey, Department of

Electronics & Communication Engineering, Delhi Technological University, Delhi and

Dr. Deva Nand, Department of Electronics & Communication Engineering, Delhi

Technological University, Delhi and is hereby submitted for the award of the degree of Doctor

of Philosophy in Department of Electronics & Communication, Delhi Technological

University, Delhi.

I further undertake that the work embodied in this thesis has not been submitted for the award

of any other degree or diploma elsewhere.

Neetika Yadav

2K18/PhD/EC/514

ii

### **ACKNOWLEDGMENT**

I extend my deepest gratitude to Prof. Neeta Pandey and Dr. Deva Nand, my esteemed supervisors from Department of Electronics and Communication Engineering (ECE), Delhi Technological University (DTU). Their expert mentorship, constant encouragement, and commitment to academic excellence have indelibly shaped my research's trajectory and quality. The faculty and staff of ECE Department have provided a vibrant academic ecosystem, equipping me with resources and opportunities for intellectual growth. The collaborative spirit within the department and the unwavering support of fellow students have been invaluable.

My colleagues and seniors from the ECE department, particularly Dr. Ranjana Sivaram, Ms. Damyanti, Ms. Sweta, and Ms. Garima, deserve my sincere appreciation for their enduring support.

I am profoundly thankful to my parents and my mother-in-law for their unwavering love and sacrifices that have been my driving force. My husband, Anand, has been an unwavering pillar of encouragement. My siblings' shared experiences have enriched my perspective, and special thanks to my lovely daughter, Zoe, who has displayed remarkable patience during my absence. My family and friends have been my bedrock of support, providing unwavering encouragement and belief during challenging times. While their names may not appear here, their impact on my academic journey is profound. This achievement is a collaborative endeavour, showcasing the contributions of numerous individuals. To all of you, I convey my heartfelt appreciation.

Neetika Yadav

Necti K9

### **ABSTRACT**

In the past decade, technological advancements in Very Large Scale Integration (VLSI) have increased integration density, pushing power to its limits and challenging packaging and cooling systems. The increasing demand for portable devices, notably smartphones, and the expanding adoption of Internet of Things (IoT) necessitate faster, power-efficient devices with extended battery life. As a result, it's crucial to develop energy efficient designs that offer improved performance.

Static CMOS and dynamic domino designs have long dominated the digital arena, yet they have inherent limitations. Static CMOS faces challenges like increased input capacitance, limiting its energy efficiency as fan-in values rise. Dynamic domino design offers lower delay but at the cost of higher energy and sensitivity to process variations. Therefore, balancing power and speed in CMOS gate remain challenging due to energy-delay trade-off.

To overcome these challenges, there is a growing need to search for logic styles and transistor technologies that can act as an alternative to existing CMOS based designs. Additionally, implementing power reduction techniques becomes imperative for these alternative logic styles to have less power. One such alternative logic style is Dual Mode Logic (DML) which offers dual mode functionality, i.e. static mode and dynamic mode, with low power and high speed. However, limited study has been conducted to reduce leakage power in the context of DML circuits. Therefore, leakage reduction techniques i.e. LECTOR and GALEOR are incorporated in footed DML design. Three designs are proposed, namely LECTOR with Dual Mode Logic (LDML), GALEOR with Dual Mode Logic (GDML) and

GALEOR with Dual Mode Logic with footed Diode (GDMLD), to reduce leakage in footed DML design. These designs use the concept of stacking to achieve leakage power reduction.

Other than this, Dual Mode Transmission Gate Diffusion Input (DMTGDI) and Differential Cascode Voltage Switch Logic (DCVSL) are alternative logic styles that can also be explored for Power Delay Product (PDP) reduction. Two such designs- Modified Dual Mode TGDI (M-DMTGDI) and Dual Mode DCVSL (DM-DCVSL) are introduced in this work which offers dual mode functionality along with PDP reduction. In addition to this, the proposed M-DMTGDI design also overcomes the contention issue present in the existing DMTGDI design.

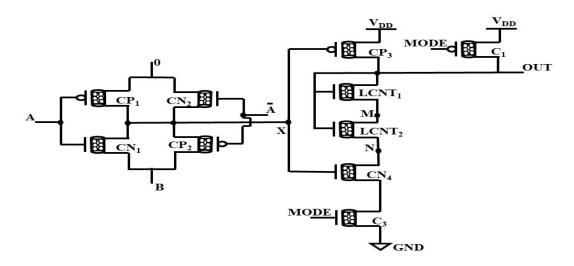

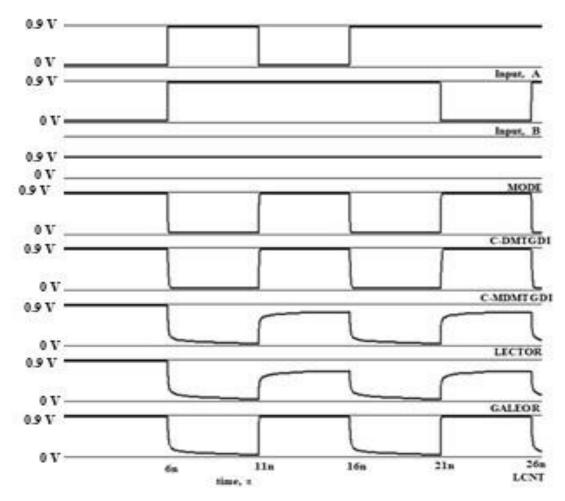

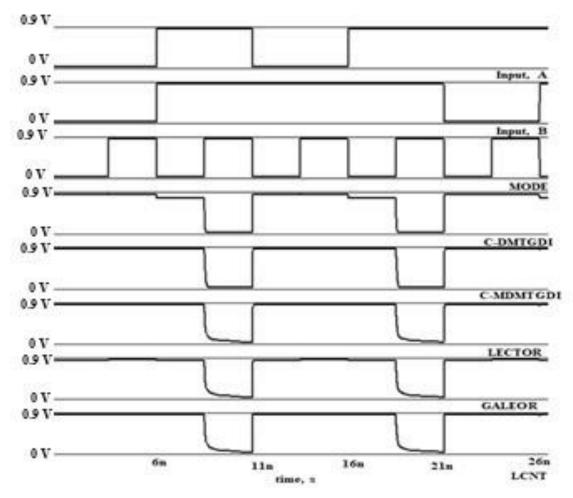

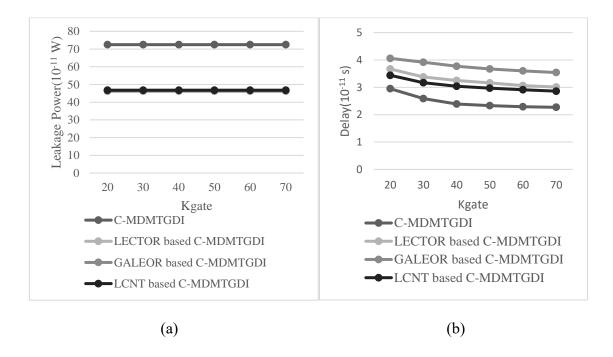

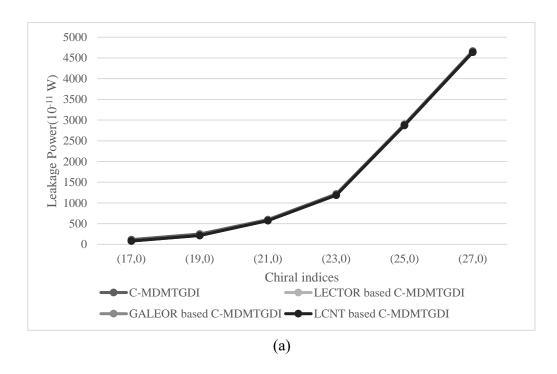

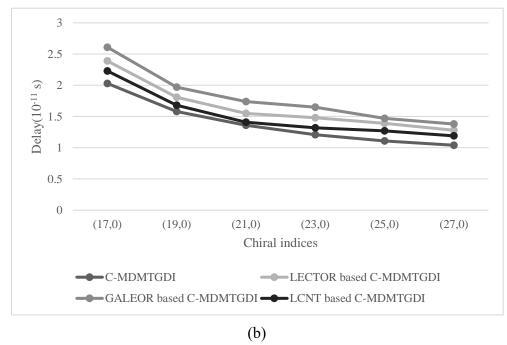

Further the improved transistor technology, primarily Carbon Nanotube Field-Effect Transistor (CNTFET), can be explored to implement designs, which already exist in MOSFET domain, so as to leverage the benefits of CNTFETs for their implementation. Such designs are put forward in this work, namely, CNTFET based footed DML (C-DML), CNTFET based DMTGDI (C-DMTGDI) and CNTFET based M-DMTGDI (C-MDMTGDI). These designs demonstrate superior performance over their CMOS counterparts, particularly in terms of reducing the PDP. Another area of research that has emerged in CNTFET domain is leakage power. Limited study has been conducted on the implementation of leakage reduction techniques in CNTFETs, using the methods previously developed for MOSFETs. So, for leakage reduction, three leakage reduction techniques namely LECTOR, GALEOR, and LCNT are also proposed for C-MDMTGDI design. Each of these proposed techniques significantly reduces leakage power but at the cost of delay.

In this thesis, the performance of all the proposed designs is analysed and compared with existing counterparts in terms of power, delay and PDP. Functional verification is done

for all proposed designs. The MOSFET based designs are simulated using Symica DE tool and HSPICE tool is used for simulating CNTFET based designs.

## TABLE OF CONTENTS

| CERTIFICATE                                                      | i    |

|------------------------------------------------------------------|------|

| DECLARATION                                                      | ii   |

| ACKNOWLEDGMENT                                                   | .iii |

| ABSTRACT                                                         | .iv  |

| TABLE OF CONTENTS                                                | vii  |

| LIST OF FIGURES                                                  | .xi  |

| LIST OF TABLES                                                   | кiх  |

| Chapter 1 Introduction                                           | 1    |

| 1.1 Background                                                   | 2    |

| 1.2 Available Literature and Scope of Work                       | 4    |

| 1.2.1 State of the art- Power reduction in standard CMOS designs | 4    |

| 1.2.2 State of the art- Alternative Logic Styles                 | 10   |

| 1.2.3 State of the art- Improved Transistor Technology           | 12   |

| 1.3 Research Gaps                                                | 14   |

| 1.4 Research Objectives                                          | 15   |

| 1.5 Organization of the thesis                                   | 17   |

| Chapter 2 Alternative Logic Styles: Basic Concepts               | 19   |

| 2.1 Introduction                                                 | 20   |

| 2.2 Dual Mode Logic (DML)                                        | 20   |

| 2.2.1 DML fundamentals                                       | 20          |

|--------------------------------------------------------------|-------------|

| 2.2.2 Operation of DML 2-input NAND gate                     | 22          |

| 2.3 Dual Mode Transmission Gate Diffusion Input (DMTGDI)     | 26          |

| 2.3.1 DMTGDI fundamentals                                    | 27          |

| 2.3.2 Operation of DMTGDI 2-input NAND gate                  | 29          |

| 2.4 Differential Cascode Voltage Switch Logic (DCVSL)        | 31          |

| 2.4.1 DCVSL fundamentals                                     | 32          |

| 2.4.2 Operation of DCVSL 2-input NAND/AND gate               | 35          |

| 2.5 Conclusion                                               | 37          |

| Chapter 3 DML Design With Leakage Power Reduction            | 38          |

| 3.1 Introduction                                             | 39          |

| 3.2 Leakage power in footed DML design                       | 40          |

| 3.3 Proposed Design-I: LECTOR with DML logic (LDML)          | 42          |

| 3.3.1 Operation                                              | 42          |

| 3.3.2 Simulation results                                     | 45          |

| 3.4 Proposed Design-II: GALEOR based DML logic (GDML) and GA | ALEOR based |

| DML logic with footed Diode (GDMLD)                          | 63          |

| 3.4.1 Operation                                              | 63          |

| 3.4.2 Simulation results                                     | 68          |

| 3.5 Conclusion                                               | 86          |

| Chapter 4 Modified DMTGDI and Dual Mode DCVSL Design      | 88         |

|-----------------------------------------------------------|------------|

| 4.1 Introduction                                          | 89         |

| 4.2 Proposed Design-III: M-DMTGDI                         | 89         |

| 4.2.1 Operation                                           | 93         |

| 4.2.2 Simulation results                                  | 96         |

| 4.3 Proposed Design-IV: Dual Mode DCVSL                   | 105        |

| 4.3.1 Operation                                           | 106        |

| 4.3.2 Simulation results                                  | 110        |

| 4.4 Conclusion                                            | 120        |

| Chapter 5 Improved Transistor Technology Based Designs    | 122        |

| 5.1 Introduction                                          | 123        |

| 5.2 Improved transistor technology- CNTFET overview       | 123        |

| 5.3 Proposed Design-V: CNTFET based DML (C-DML)           | 125        |

| 5.3.1 Operation                                           | 127        |

| 5.3.2 Simulation results                                  | 131        |

| 5.4 Proposed Design-VI: CNTFET based M-DMTGDI (C-MDMTGDI) | 143        |

| 5.4.1 Operation                                           | 143        |

| 5.4.2 Simulation results                                  | 146        |

| 5.5 Proposed Design-VII: LECTOR based C-MDMTGDI, GA       | LEOR based |

| C-MDMTGDI and LCNT based C-MDMTGDI                        | 157        |

| 5.5     | 5.1 Operation          | 158 |

|---------|------------------------|-----|

| 5.5     | 5.2 Simulation results | 161 |

| 5.6     | Conclusion             | 170 |

| Chapte  | r 6 Conclusion         | 173 |

| 6.1     | Concluding Remarks     | 174 |

| 6.2     | Future Work            | 177 |

| Referer | nces                   | 178 |

| Publica | ntions                 | 193 |

## LIST OF FIGURES

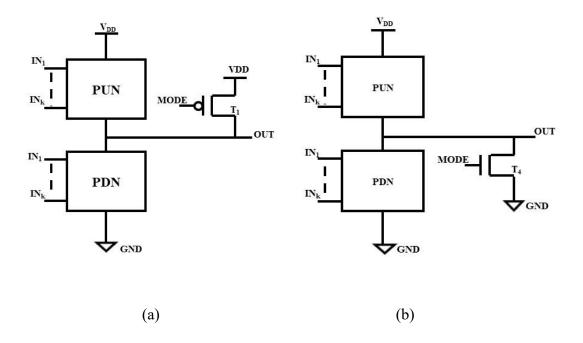

| Fig. 2.1 DML design (a) Unfooted type A [14] (b) Unfooted type B [14]21                   |

|-------------------------------------------------------------------------------------------|

| Fig. 2.2 DML design (a) Footed type A [14] (b) Footed type B [14]22                       |

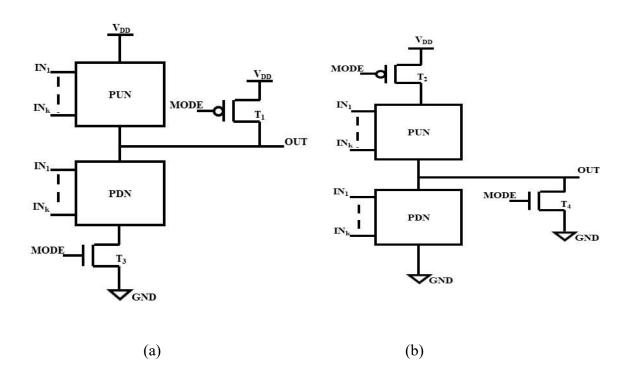

| Fig. 2.3 DML based 2-input NAND gate (a) Unfooted type A (b) Unfooted type B24            |

| Fig. 2.4 DML based 2-input NAND gate (a) Footed type A (b) Footed type B25                |

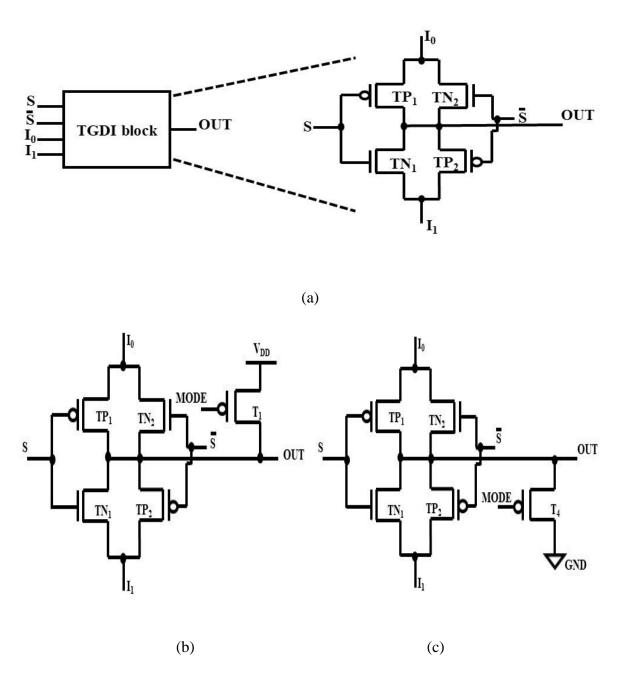

| Fig. 2.5 (a) TGDI block and its internal structure (b) Type A DMTGDI cell [17] (c) Type B |

| DMTGDI cell [17]                                                                          |

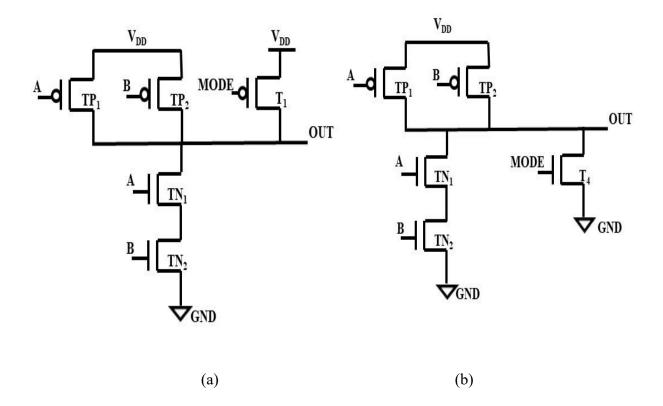

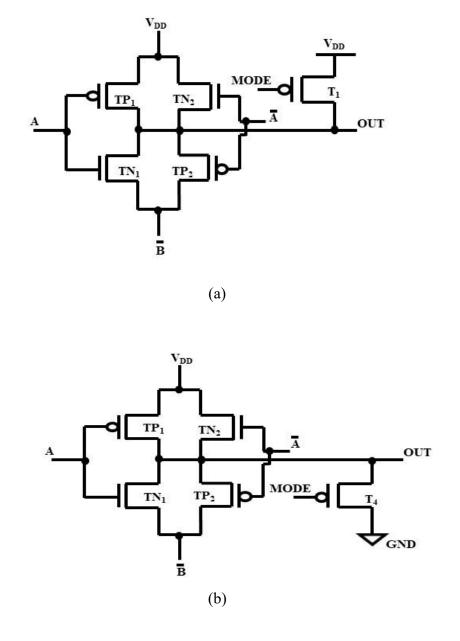

| Fig. 2.6 DMTGDI based 2-input NAND gate (a) Type A (b) Type B [17]30                      |

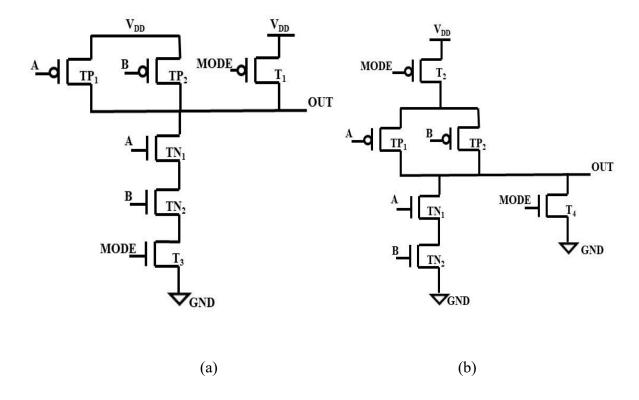

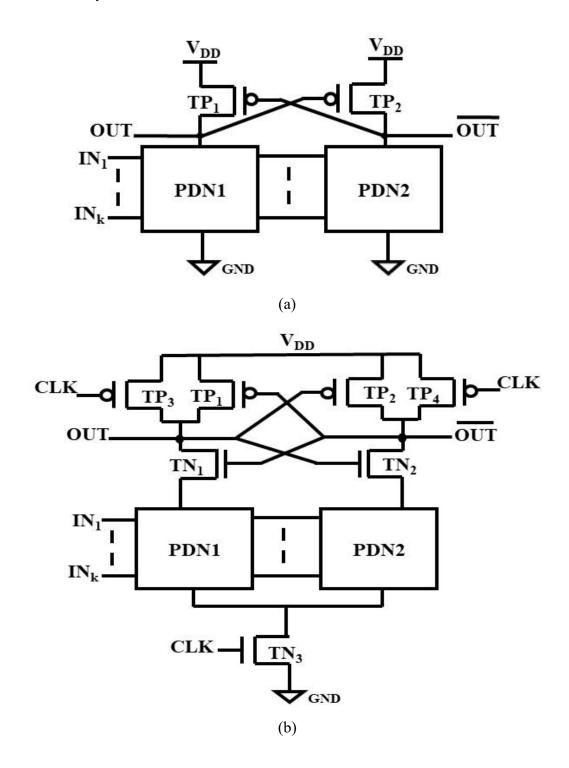

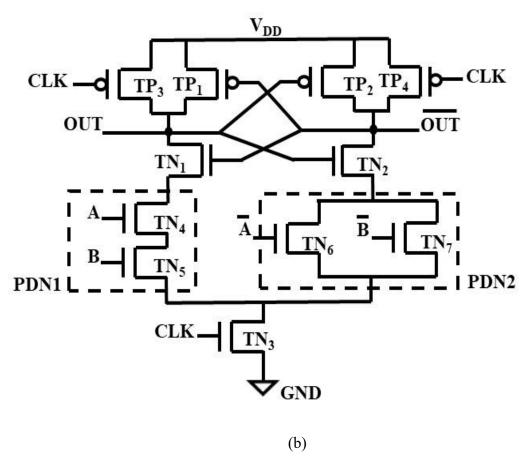

| Fig. 2.7 DCVSL design (a) Static [11] (b) Dynamic [12]                                    |

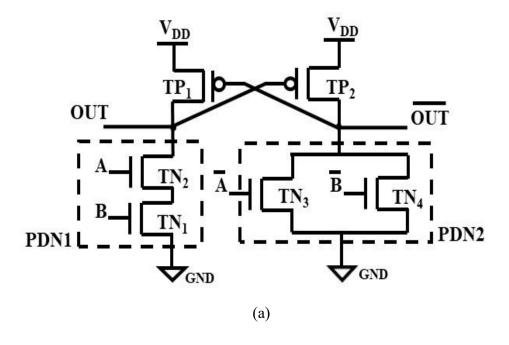

| Fig. 2.8 2-input AND/NAND gate (a) Static DCVSL [11] (b) Dynamic DCVSL [12]36             |

| Fig. 3.1 Footed DML design (a) Type A NAND gate (TA-NAND) (b) Type B NAND gate            |

| (TB-NAND)41                                                                               |

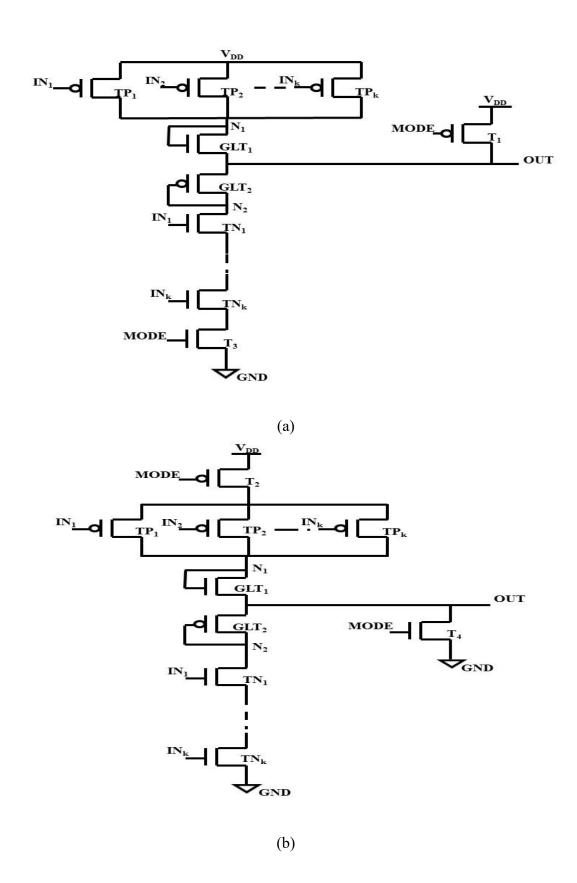

| Fig. 3.2 Proposed LDML design (a) Type A NAND gate (LDML-TA-NAND) (b) Type B              |

| NAND gate (LDML-TB-NAND)44                                                                |

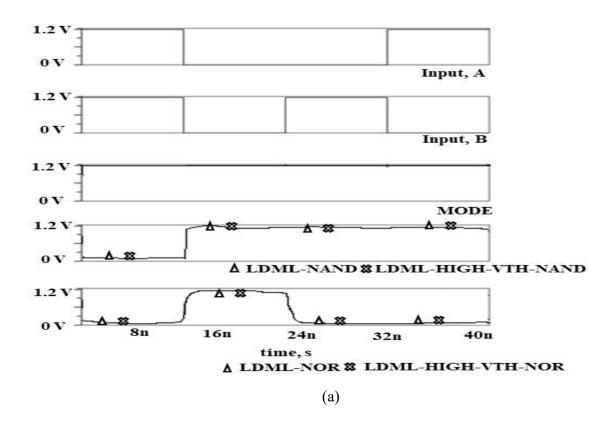

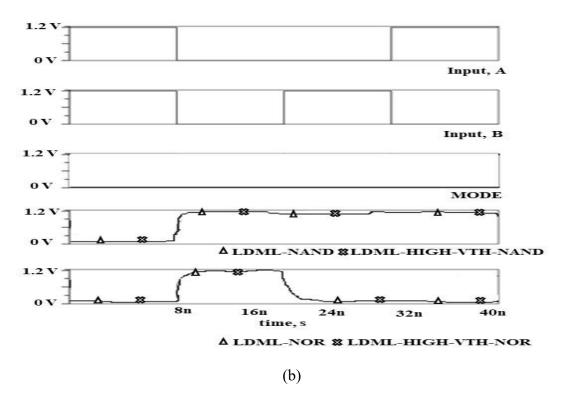

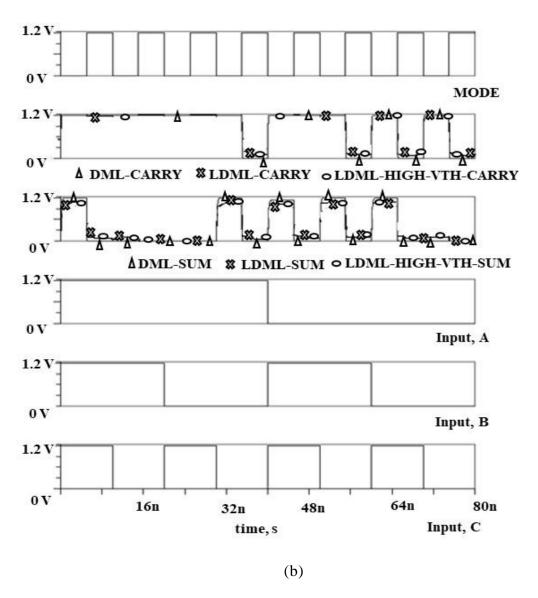

| Fig. 3.3 Transient waveforms of the proposed LDML design in static mode (a) 2-input type  |

| A NAND and NOR gate (b) 2-input type B NAND and NOR gate                                  |

| Fig. 3.4 Transient waveforms of the proposed LDML design in dynamic mode (a) 2-input      |

| type A NAND and NOR gate (b) 2-input type B NAND and NOR gate48                           |

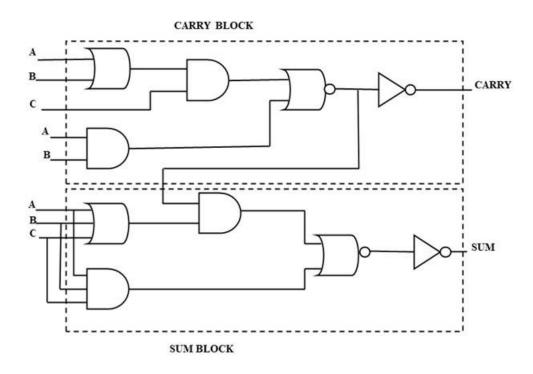

| Fig. 3.5 Schematic of a 1-bit FA design [6]                                               |

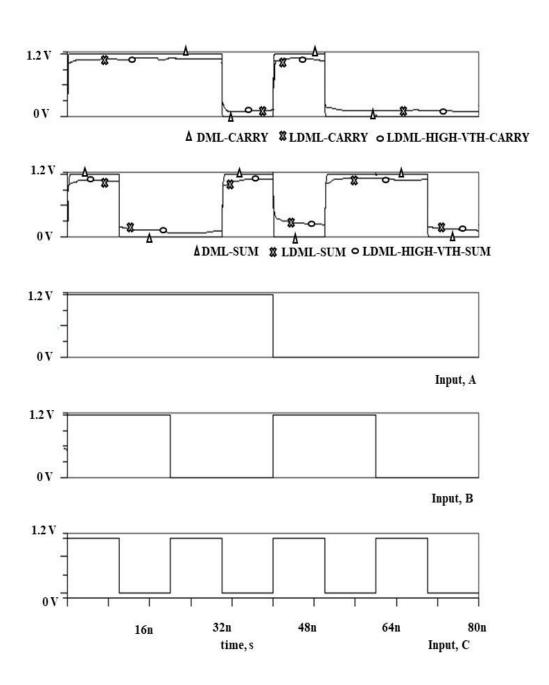

| Fig. 3.6 Transient waveform of proposed LDML based 1-bit FA (a) Static mode (b) Dynamic   |

| mode                                                                                      |

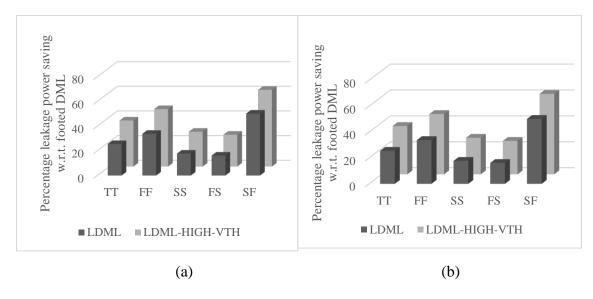

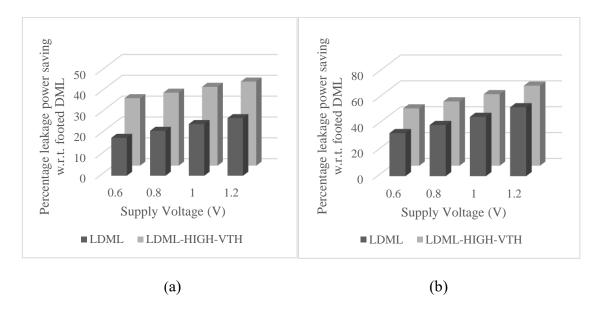

| Fig. 3.7 Percentage leakage power saving for proposed LDML based 2-input type A NAND      |

| gate at five different process corners in static mode at (a) 90nm (b) 45nm                |

| Fig. 3.8 Percentage leakage power saving for proposed LDML based 2-input type A NAND       |

|--------------------------------------------------------------------------------------------|

| gate at five different process corners in pre-charge phase of dynamic mode at (a) 90nm (b) |

| 45nm                                                                                       |

| Fig. 3.9 Percentage leakage power saving for proposed LDML based 2-input type A NAND       |

| gate at five different process corners in evaluation phase of dynamic mode at (a) 90nm (b) |

| 45nm                                                                                       |

| Fig. 3.10 Percentage leakage power saving for proposed LDML based 2-input type A NAND      |

| gate at different voltages in static mode at (a) 90nm (b) 45nm60                           |

| Fig. 3.11 Percentage leakage power saving for proposed LDML based 2-input type A NAND      |

| gate at different voltages in pre-charge phase of dynamic mode at (a) 90nm (b) 45nm61      |

| Fig. 3.12 Percentage leakage power saving for proposed LDML based 2-input type A NAND      |

| gate at different voltages in evaluation phase of dynamic mode at (a) 90nm (b) 45nm61      |

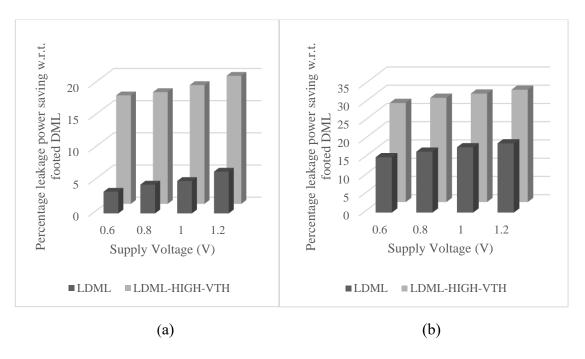

| Fig. 3.13 Effect of variation of load capacitance on leakage power for LDML based 2-input  |

| type A NAND gate (a) 90nm (b) 45nm                                                         |

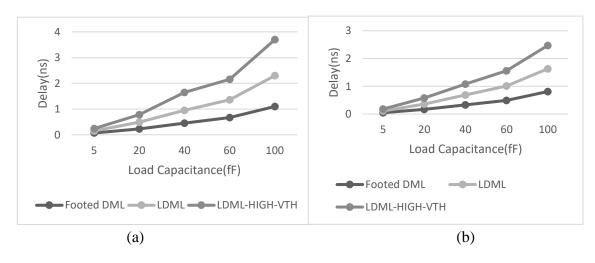

| Fig. 3.14 Effect of variation of load capacitance on delay for LDML based 2-input type A   |

| NAND gate (a) 90nm (b) 45nm                                                                |

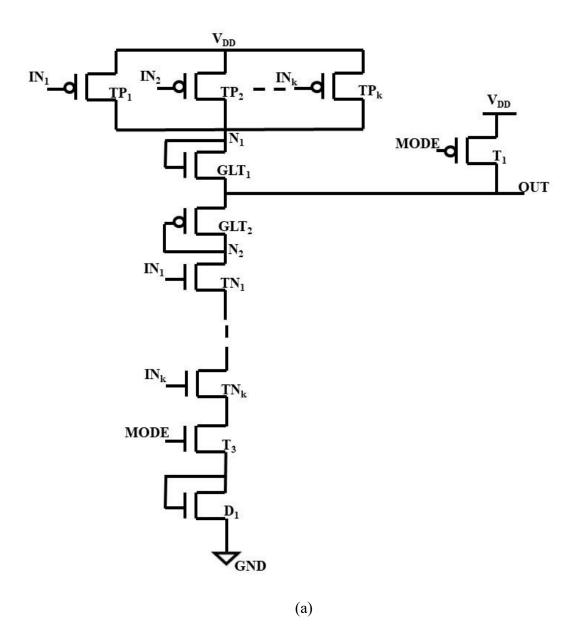

| Fig. 3.15 Proposed GDML design (a) Type A NAND gate (b) Type B NAND gate66                 |

| Fig. 3.16 Proposed GDMLD design (a) Type A NAND gate (b) Type B NAND gate68                |

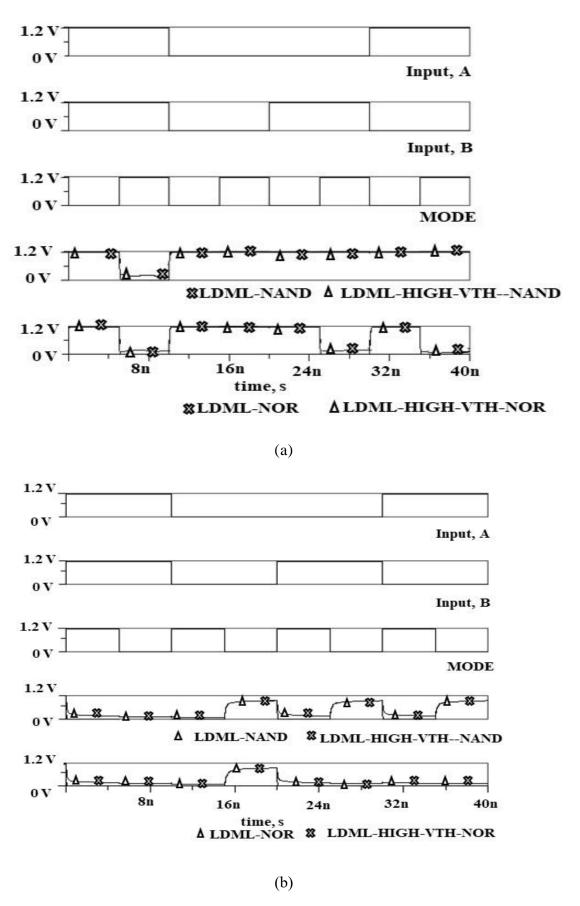

| Fig. 3.17 Transient waveforms of the proposed GDML and GDMLD design in static mode         |

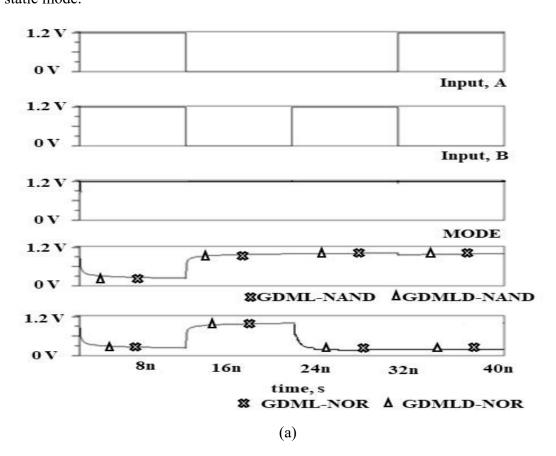

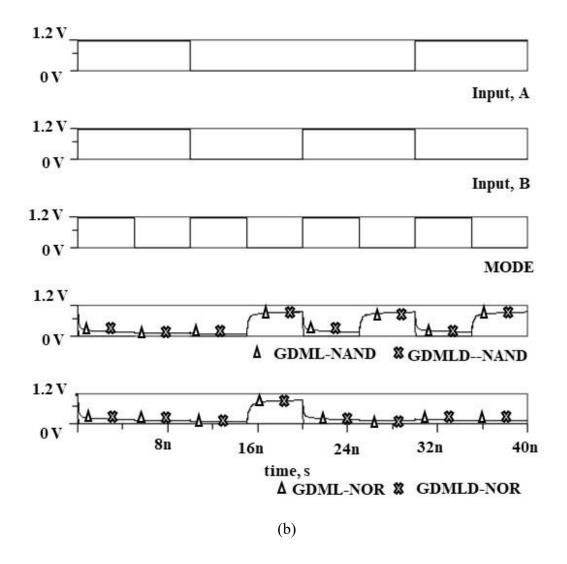

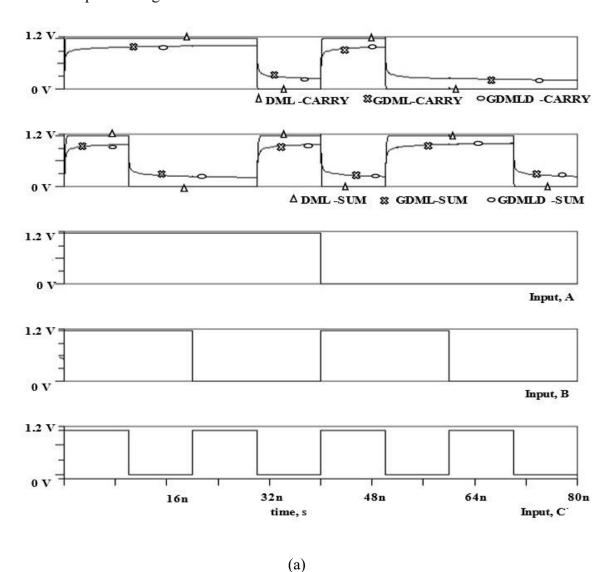

| (a) Type A NAND and NOR gate (b) Type B NAND and NOR gate70                                |

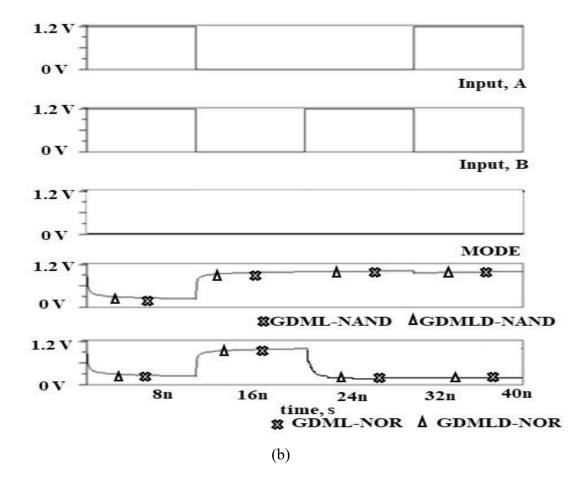

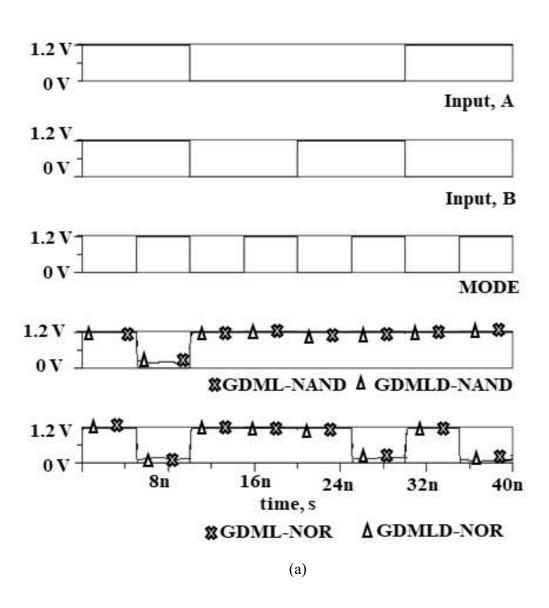

| Fig. 3.18 Transient waveforms of the proposed GDML and GDMLD design in dynamic mode        |

| (a) Type A NAND and NOR gate (b) Type B NAND and NOR gate                                  |

| Fig. 3.19 Transient waveforms of proposed GDML and GDMLD based 1-bit FA (a) Static         |

| mode (b) Dynamic mode                                                                      |

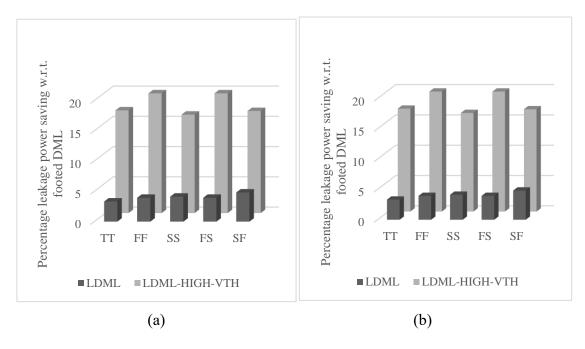

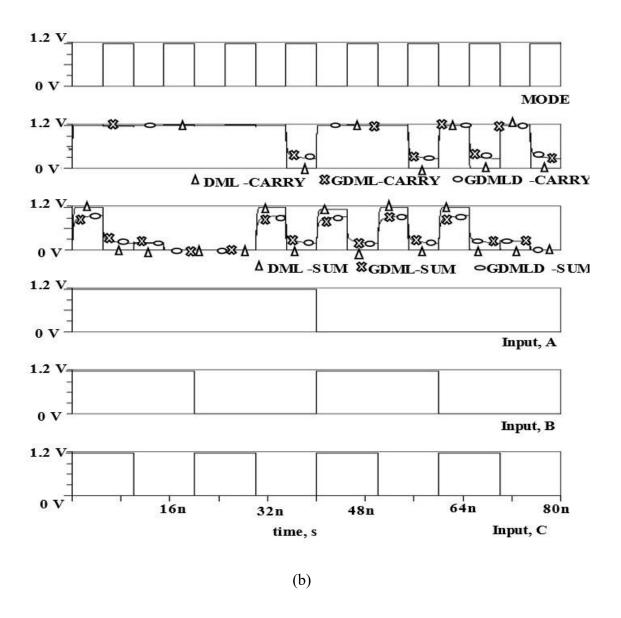

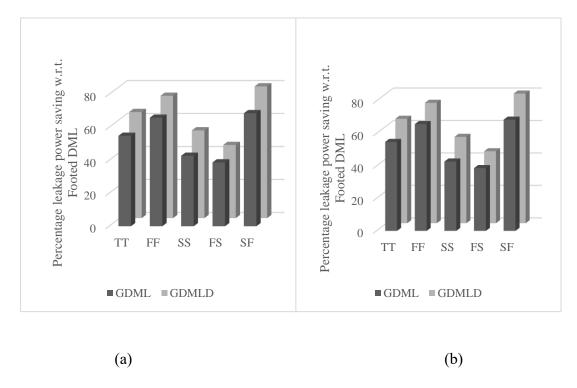

| Fig. 3.20 Percentage leakage power saving for proposed GDML and GDMLD based 2-input           |

|-----------------------------------------------------------------------------------------------|

| type A NAND gate at five different process corners in static mode at (a) 90nm (b) 45nm81      |

| Fig. 3.21 Percentage leakage power saving for proposed GDML and GDMLD based 2-inpu            |

| type A NAND gate at five different process corners in pre-charge phase of dynamic mode a      |

| (a) 90nm (b) 45nm                                                                             |

| Fig. 3.22 Percentage leakage power saving for proposed GDML and GDMLD based 2-input           |

| type A NAND gate at five different process corners in evaluation phase of dynamic mode at     |

| (a) 90nm (b) 45nm                                                                             |

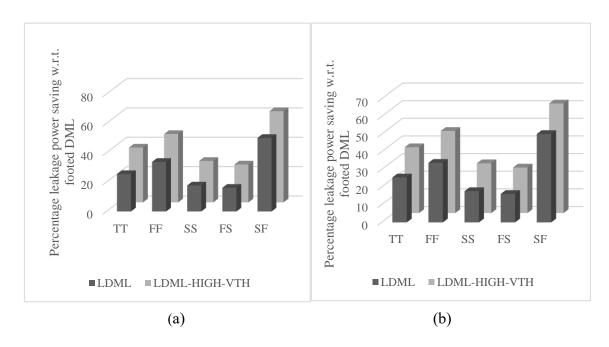

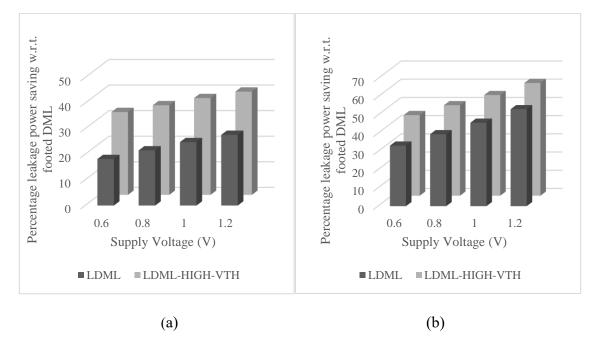

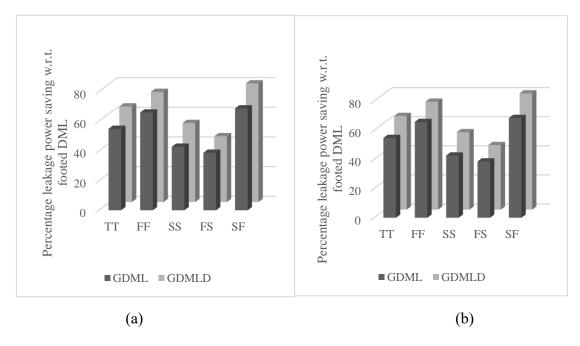

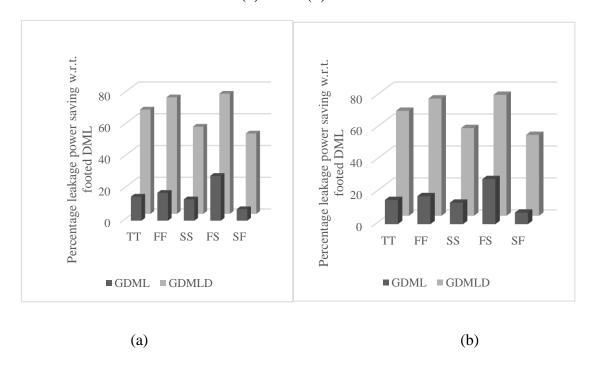

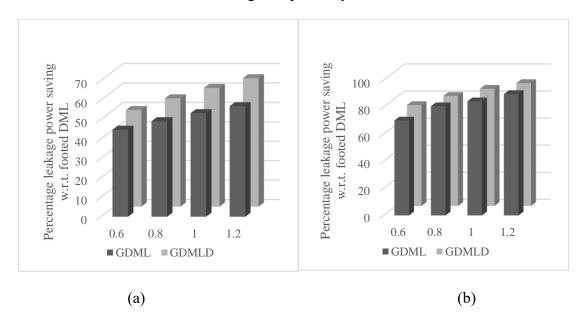

| Fig. 3.23 Percentage leakage power saving for proposed GDML and GDMLD based 2-input           |

| type A NAND gate at different voltages in static mode at (a) 90nm (b) 45nm83                  |

| Fig. 3.24 Percentage leakage power saving for proposed GDML and GDMLD based 2-input           |

| type A NAND gate at different voltages in pre-charge phase of dynamic mode at (a) 90nm        |

| (b) 45nm83                                                                                    |

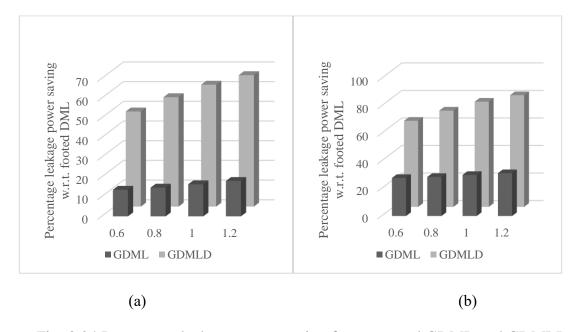

| Fig. 3.25 Percentage leakage power saving for proposed GDML and GDMLD based 2-input           |

| type A NAND gate at different voltages in evaluation phase of dynamic mode at (a) 90nm        |

| (b) 45nm84                                                                                    |

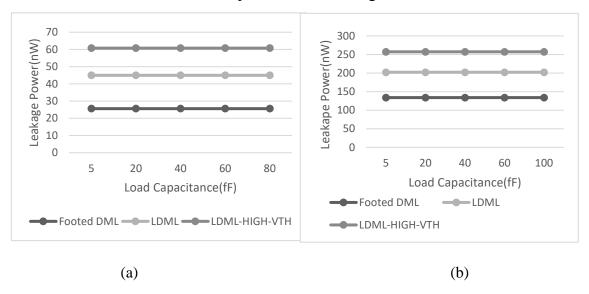

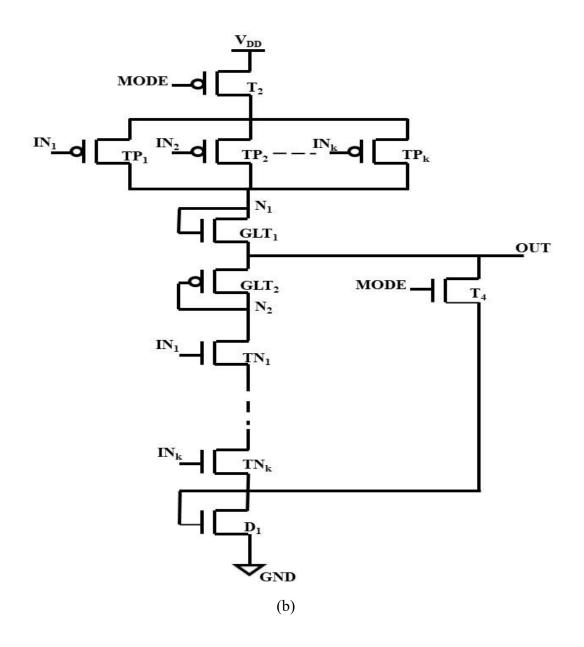

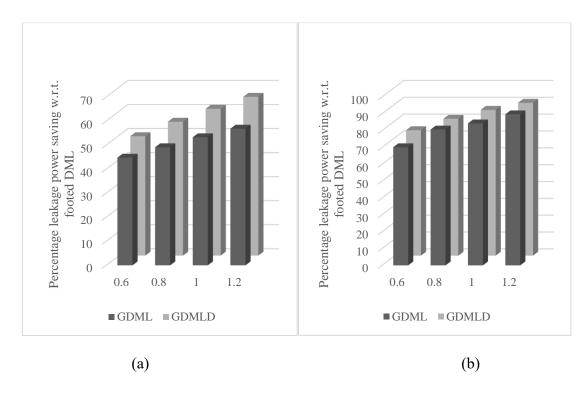

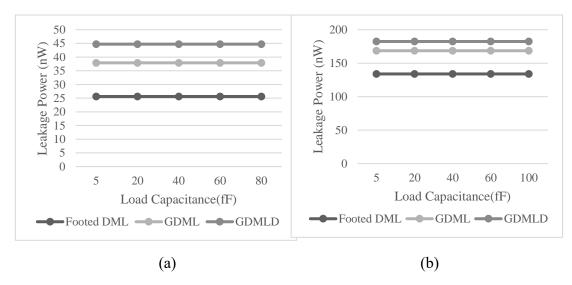

| Fig. 3.26 Effect of variation of load capacitance on leakage power for footed DML, proposed   |

| GDML and GDMLD based 2-input type A NAND gate (a) 90nm (b) 45nm85                             |

| Fig. 3.27 Effect of variation of load capacitance on delay for footed DML, proposed GDML      |

| and GDMLD based 2-input type A NAND gate (a) 90nm (b) 45nm85                                  |

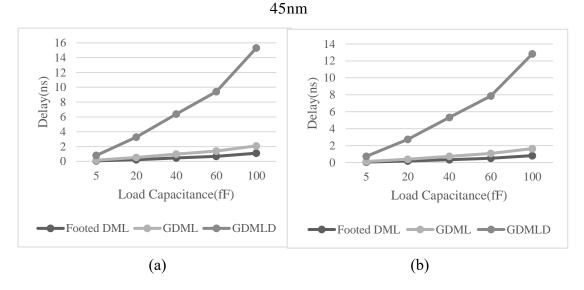

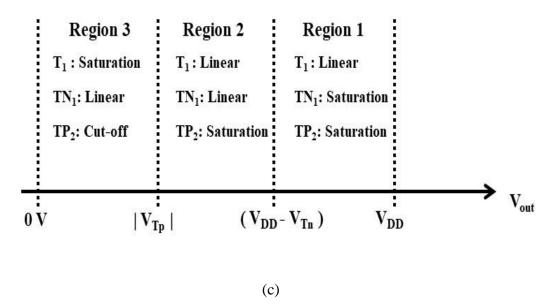

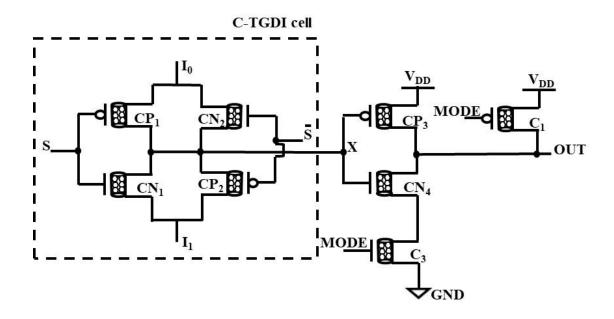

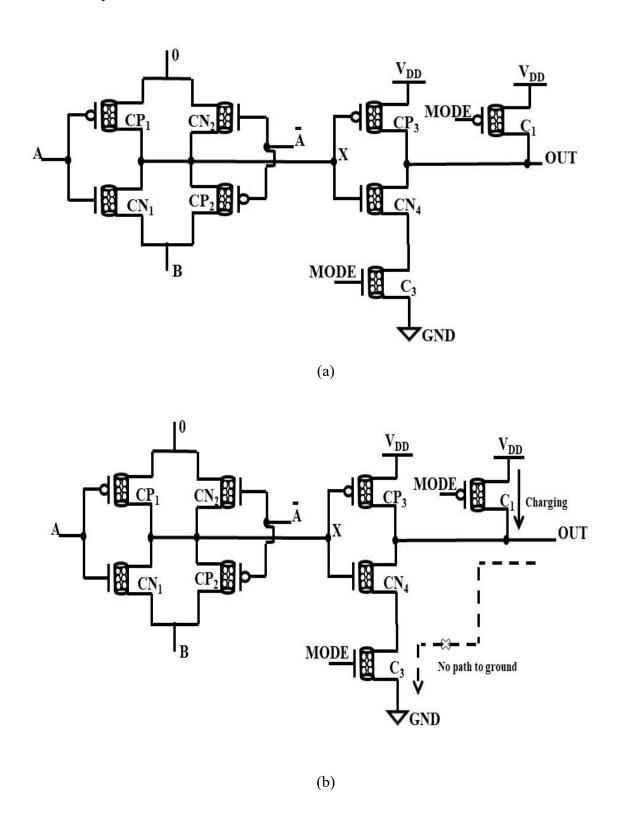

| Fig. 4.1 (a) DMTGDI based 2-input NAND gate in pre-charge phase of dynamic mode for           |

| (A, B) = (1,1) (b) Equivalent circuit of (a) (c) Bias conditions and operating regions of the |

| DMTGDI based 2-input NAND gate                                                                |

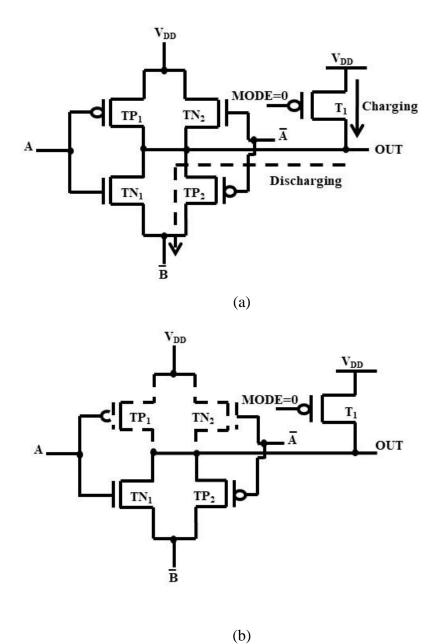

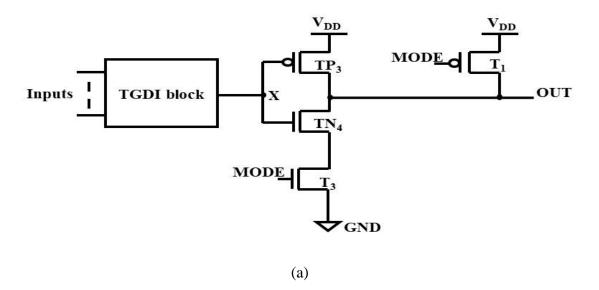

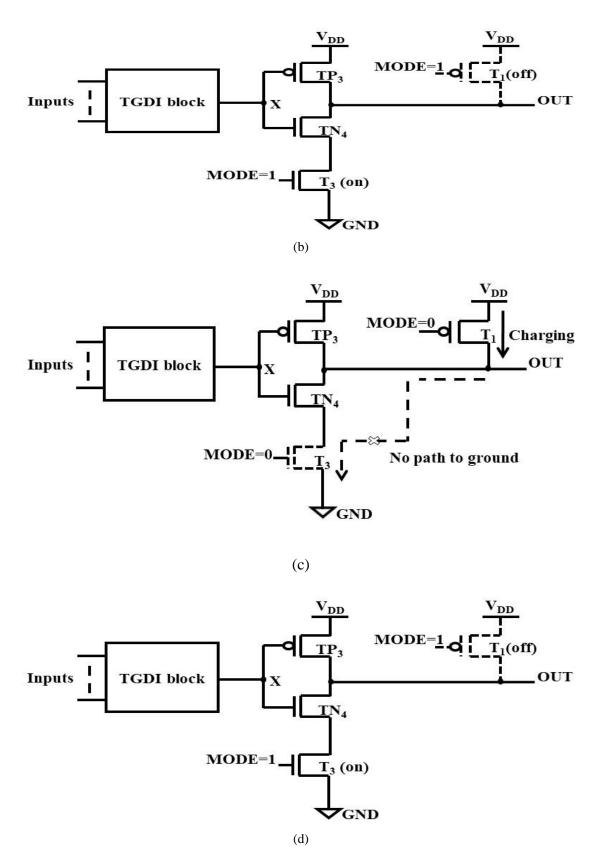

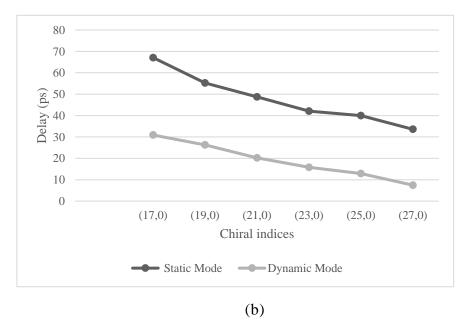

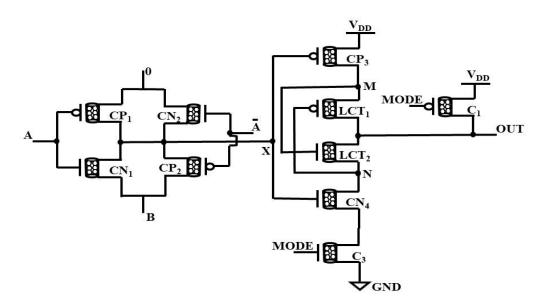

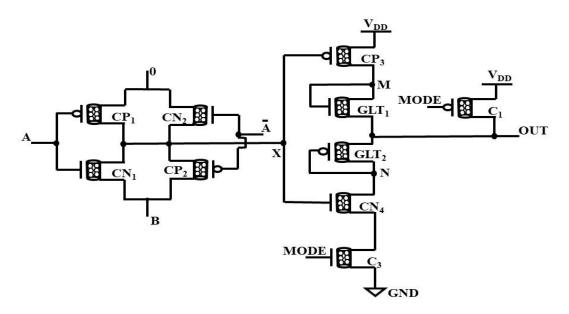

| Fig. 4.2 (a) Proposed M-DMTGDI cell (b) Proposed M-DMTGDI cell in static mode (c)               |

|-------------------------------------------------------------------------------------------------|

| Proposed M-DMTGDI cell in pre-charge phase of dynamic mode (d) Proposed M-DMTGDI                |

| cell in evaluation phase of dynamic mode                                                        |

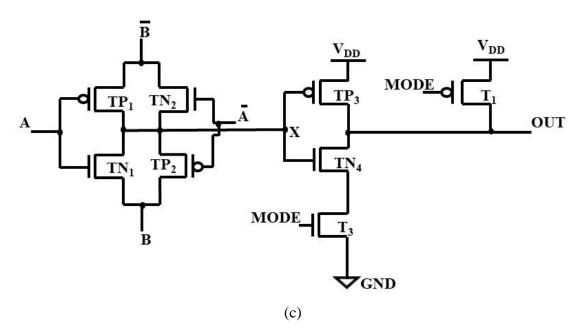

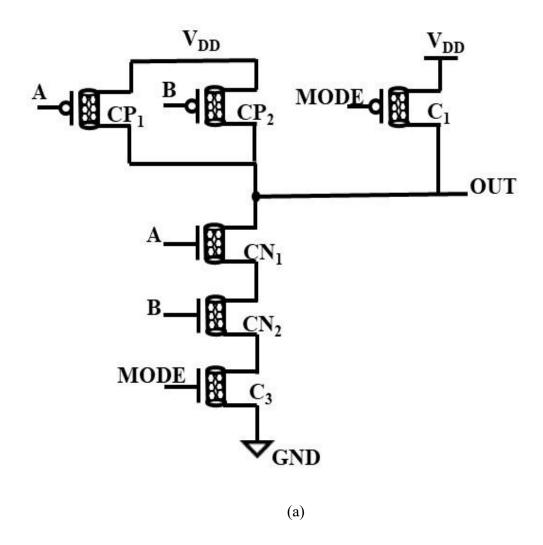

| Fig. 4.3 Proposed M-DMTGDI based gate (a) 2-input NAND gate (b) 2-input NOR gate (c)            |

| 2-input XOR gate96                                                                              |

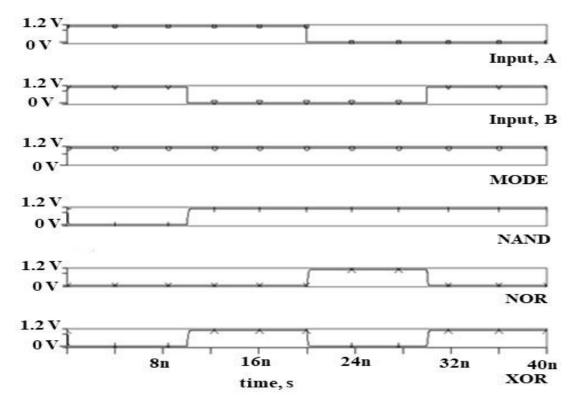

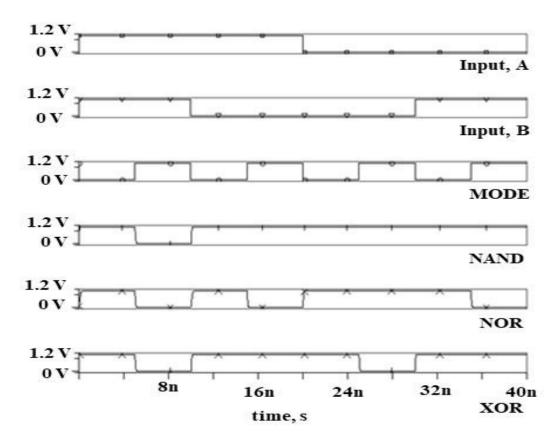

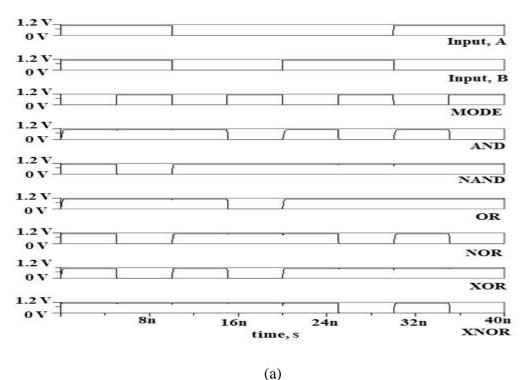

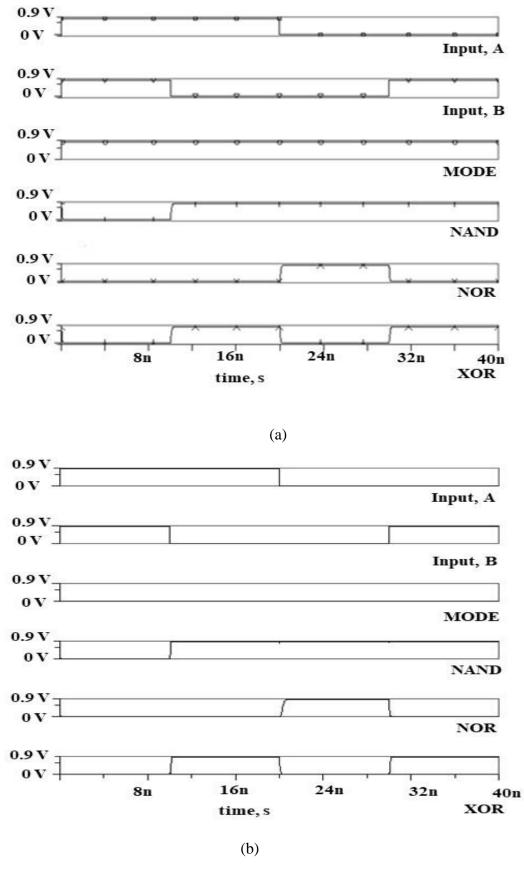

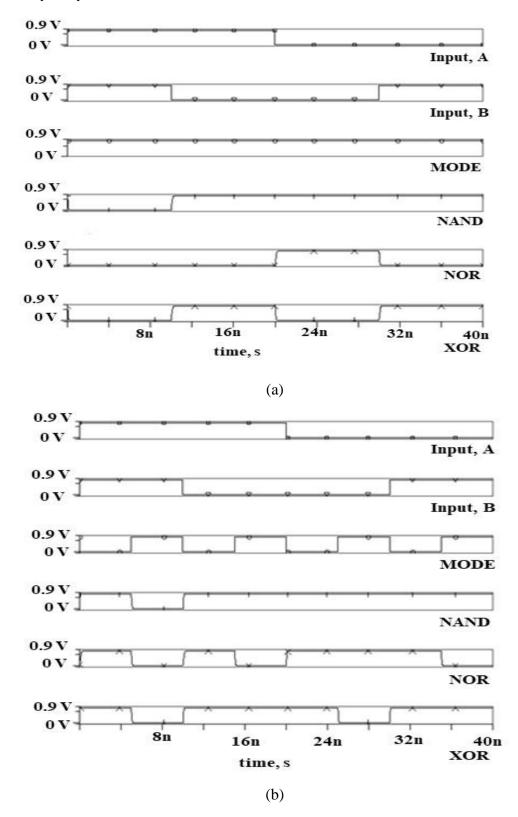

| Fig. 4.4 Transient waveforms of proposed M-DMTGDI design for 2-input gates in static            |

| mode97                                                                                          |

| Fig. 4.5 Transient waveforms of proposed M-DMTGDI design for 2-input gates in dynamic           |

| mode                                                                                            |

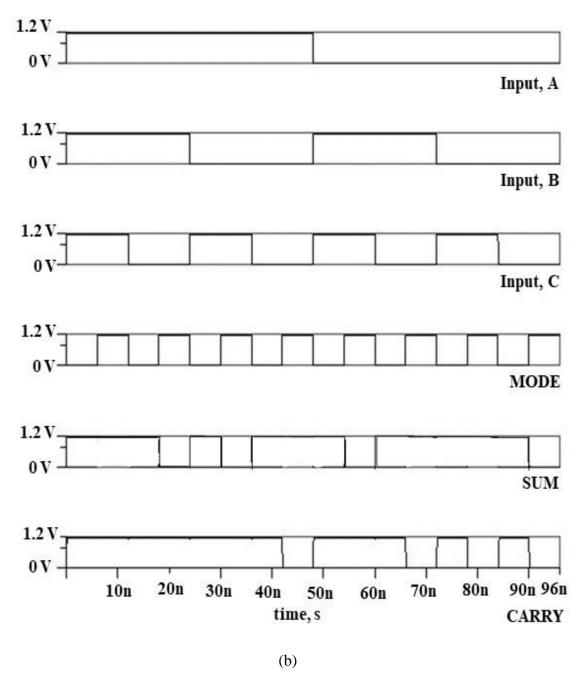

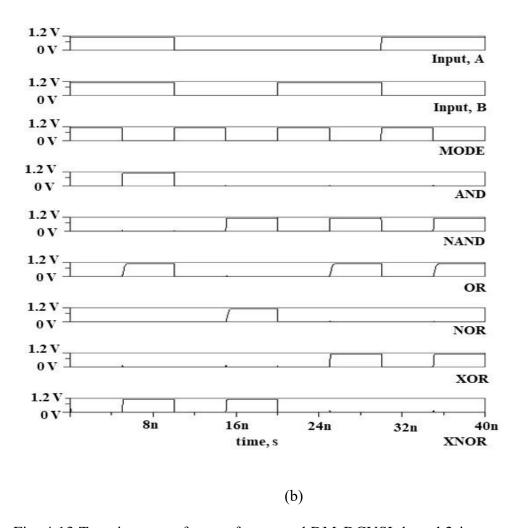

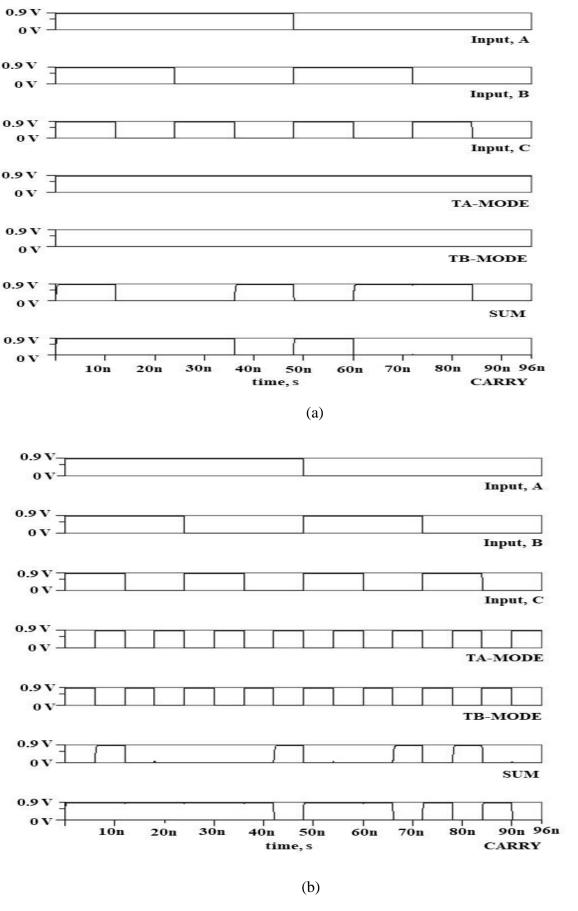

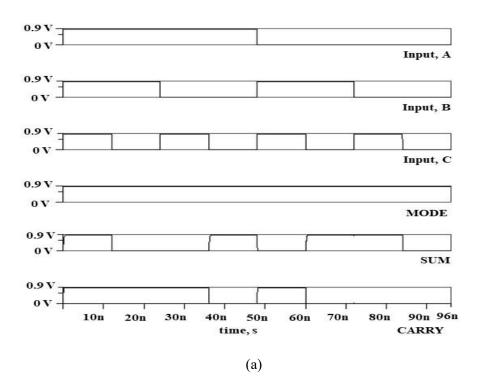

| Fig. 4.6 Transient waveforms of proposed M-DMTGDI based 1-bit FA (a) Static mode (b)            |

| Dynamic mode                                                                                    |

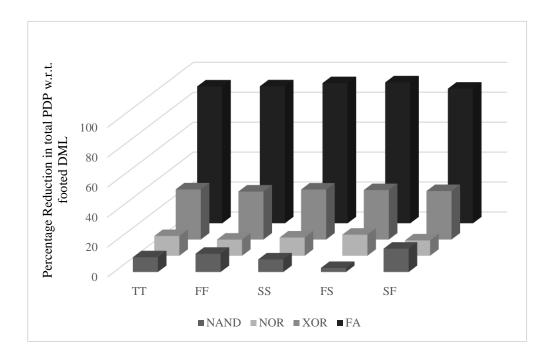

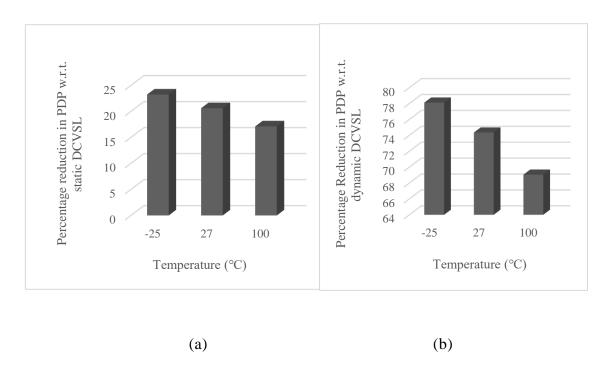

| Fig. 4.7 Percentage reduction in total PDP in both static and dynamic mode for proposed         |

| 2-input gates and 1-bit FA circuit at five different process corners (a) with respect to footed |

| DML design (b) with respect to DMTGDI design                                                    |

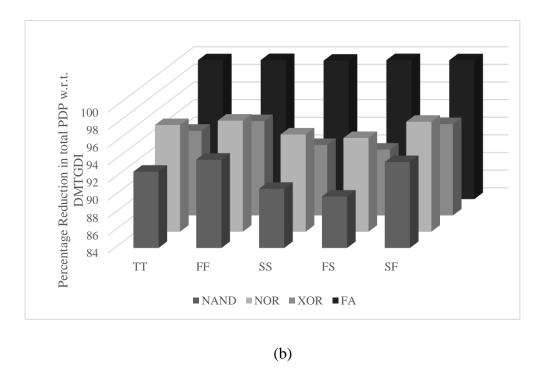

| Fig. 4.8 Percentage reduction in total PDP in both static and dynamic mode for proposed         |

| M-DMTGDI design based 2-input type A NAND gate at different voltages (a) with respect           |

| to footed DML design (b) with respect to DMTGDI design                                          |

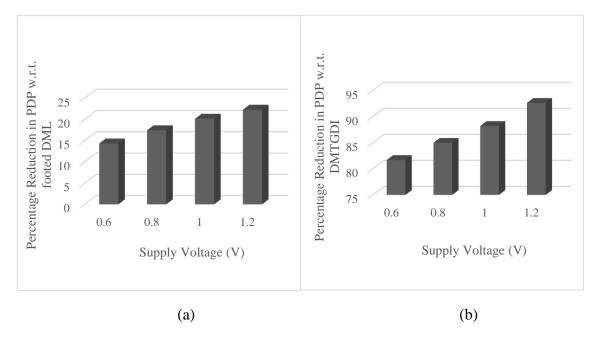

| Fig. 4.9 Percentage reduction in total PDP in both static and dynamic mode for proposed         |

| M-DMTGDI design based 2-input type A NAND gate at different temperature (a) with                |

| respect to footed DML design (b) with respect to DMTGDI design                                  |

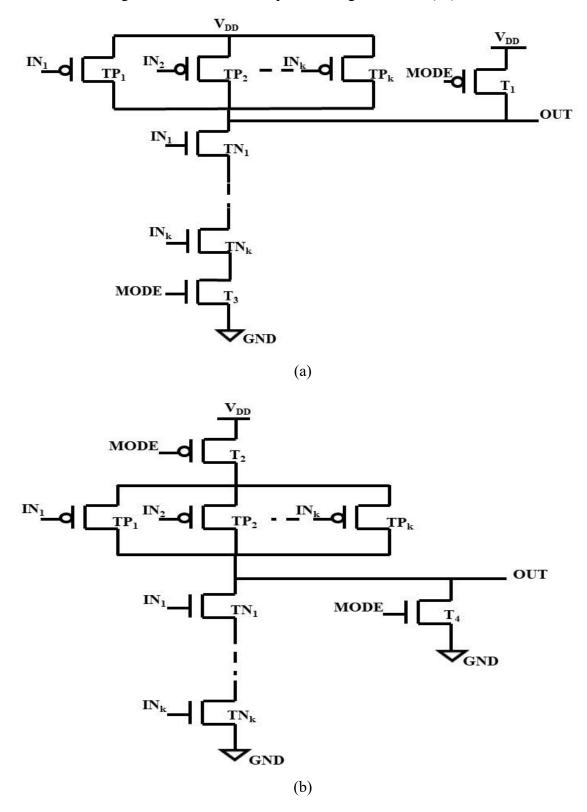

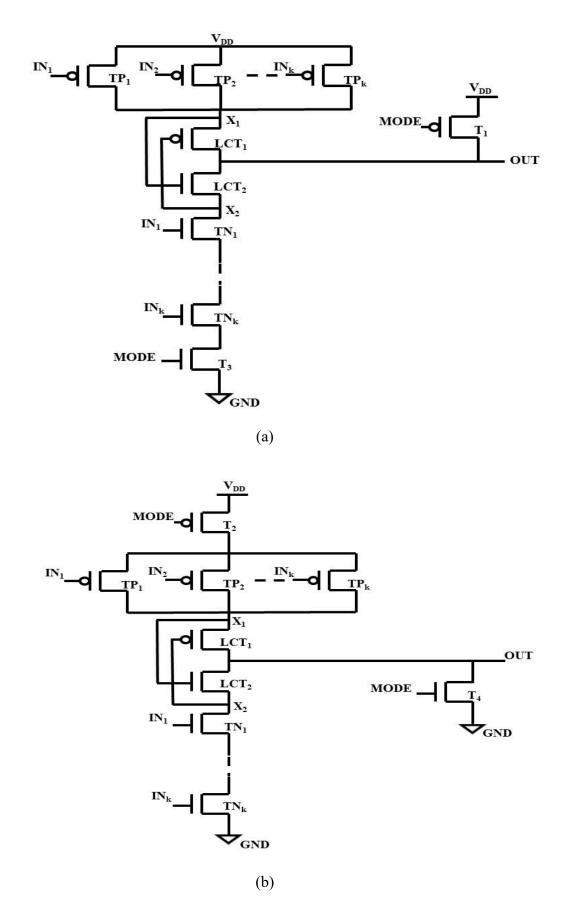

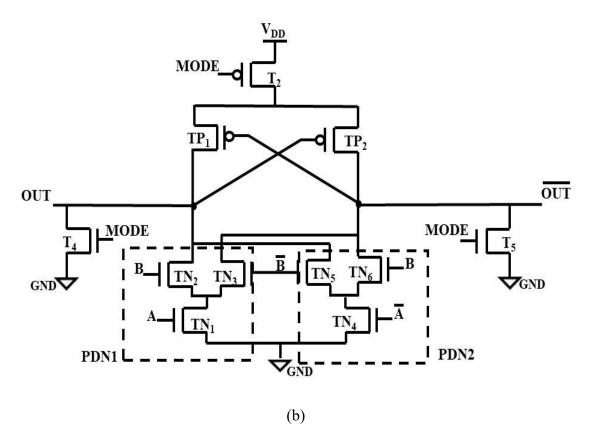

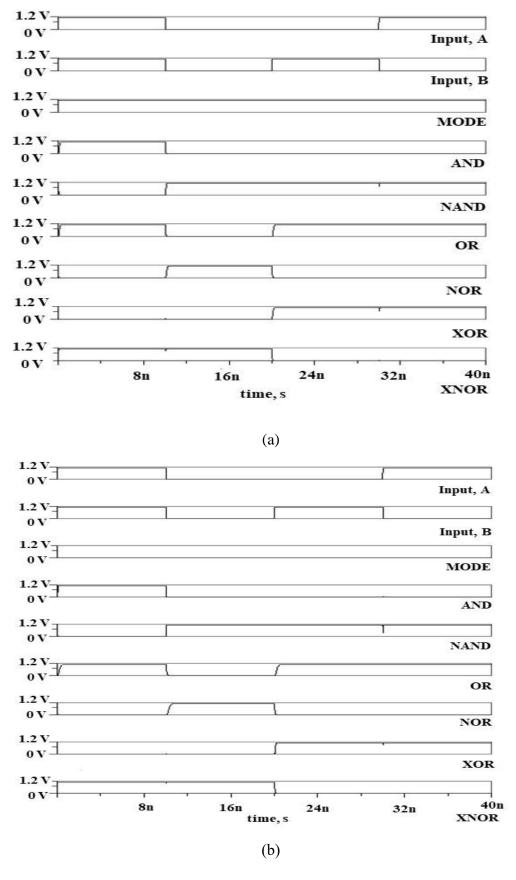

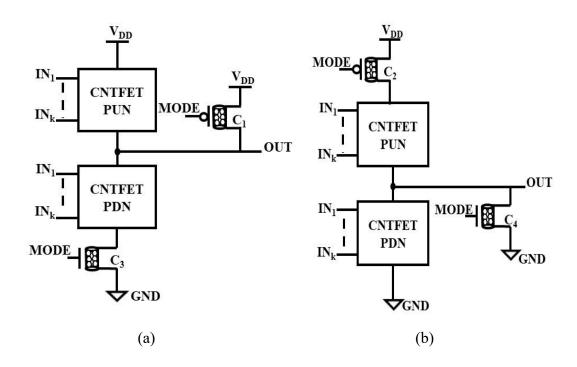

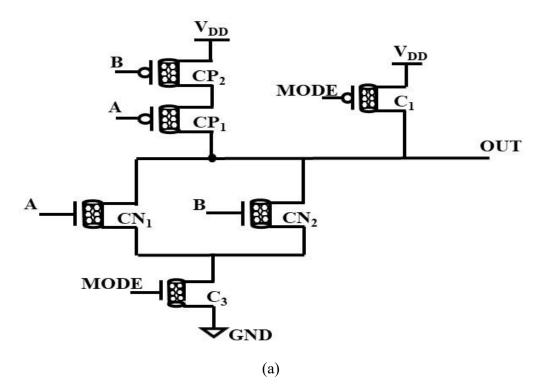

| Fig. 4.10 Proposed DM-DCVSL design (a) Type A (b) Type B                                        |

| Fig. 4.11 Proposed DM-DCVSL based 2-input XOR/XNOR gate (a) Type A (b) Type B 109               |

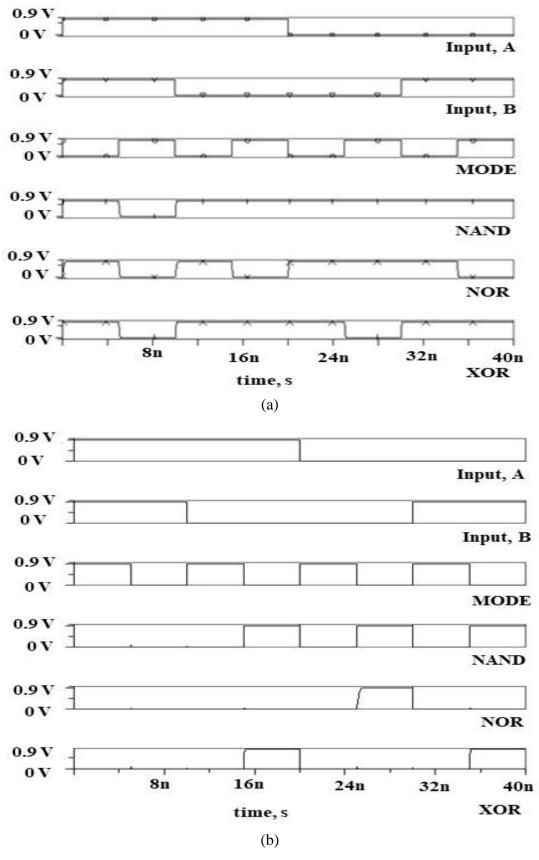

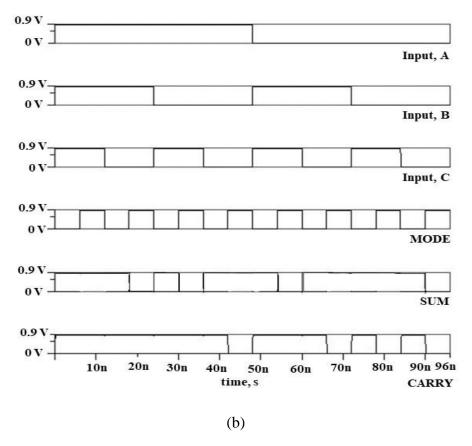

| Fig. 4.12 Transient waveforms of proposed DM-DCVSL based 2-input gates at 90nm in static        |

| mode (a) Type A (b) Type B                                                                      |

| Fig. 4.13 Transient waveforms of proposed DM-DCVSL based 2-input gates at 90nm in          |

|--------------------------------------------------------------------------------------------|

| dynamic mode (a) Type A (b) Type B                                                         |

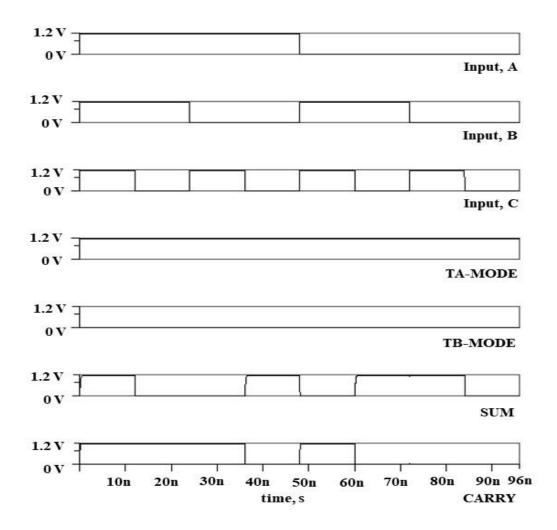

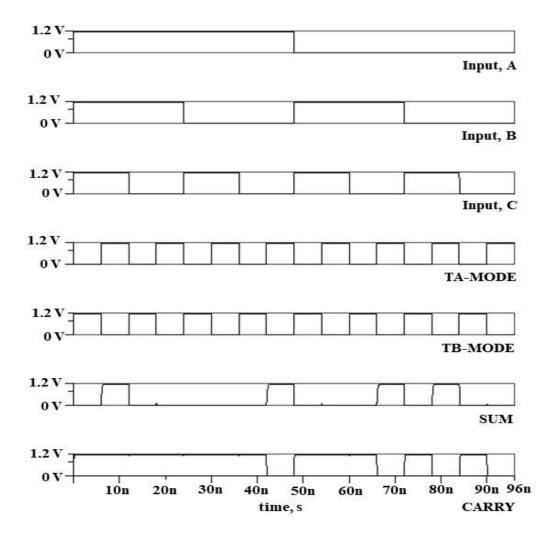

| Fig. 4.14 Transient waveforms of proposed DM-DCVSL based 1-bit FA in static mode 114       |

| Fig. 4.15 Transient waveforms of proposed DM-DCVSL based 1-bit FA in dynamic mode          |

|                                                                                            |

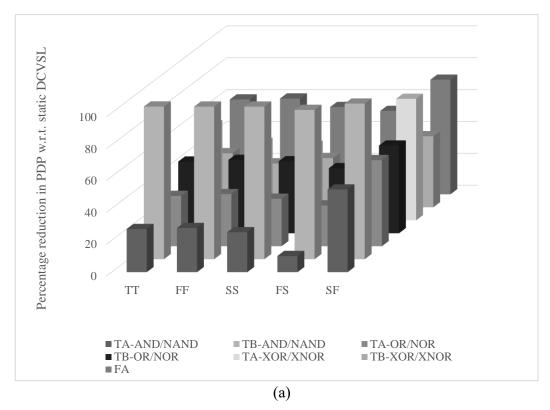

| Fig. 4.16 Percentage reduction in PDP for proposed 2-input gates at five different process |

| corners (a) Static mode w.r.t. static DCVSL (b) Dynamic mode w.r.t. dynamic DCVSL 118      |

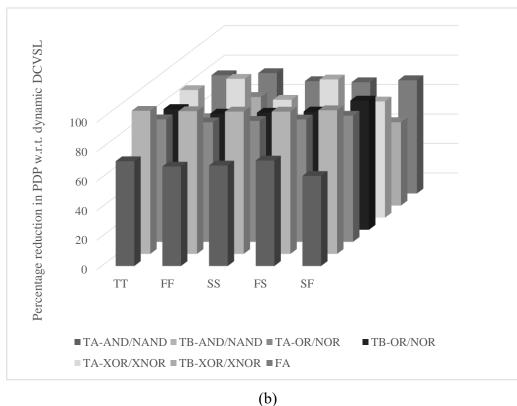

| Fig. 4.17 Percentage reduction in PDP for proposed DM-DCVSL based 2-input type A           |

| AND/NAND gate at different voltages (a) Static mode (b) Dynamic mode119                    |

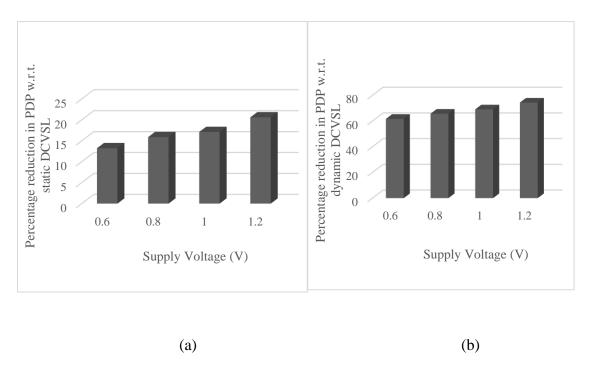

| Fig. 4.18 Percentage reduction in PDP for proposed DM-DCVSL based 2-input type A           |

| AND/NAND gate at different temperatures (a) Static mode (b) Dynamic mode120                |

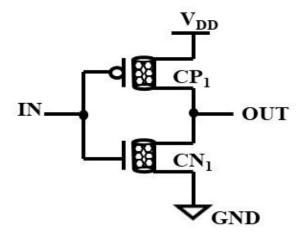

| Fig. 5.1 Standard CNTFET based inverter [117]                                              |

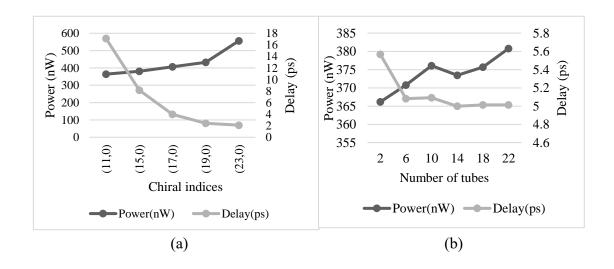

| Fig. 5.2 Power and delay for standard CNTFET based inverter at 32nm with variation in      |

| (a) Chiral indices (b) Number of tubes                                                     |

| Fig. 5.3 Proposed C-DML design (a) Type A (b) Type B                                       |

| Fig. 5.4 Proposed C-DML based 2-input NAND gate (a) Type A (b) Type B129                   |

| Fig. 5.5 Proposed C-DML based 2-input NOR gate (a) Type A (b) Type B                       |

| Fig. 5.6 Proposed C-DML based 2-input XOR gate (a) Type A (b) Type B131                    |

| Fig. 5.7 Transient waveforms of proposed C-DML based 2-input gates at 32nm in static mode  |

| (a) Type A (b) Type B                                                                      |

| Fig. 5.8 Transient waveforms of proposed C-DML based 2-input gates at 32nm in dynamic      |

| mode (a) Type A (b) Type B                                                                 |

| Fig. 5.9 Transient waveforms of proposed C-DML based 1-bit FA (a) Static mode              |

| (b) Dynamic mode                                                                           |

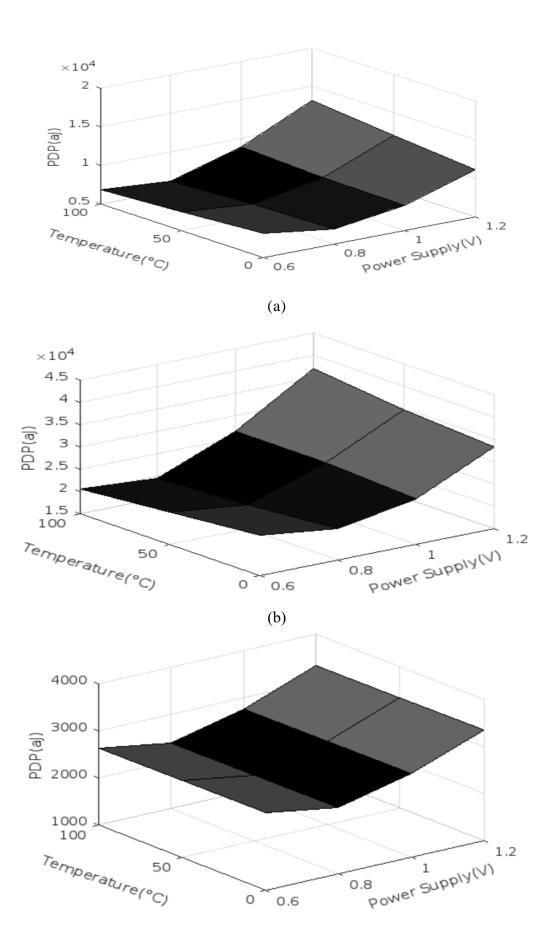

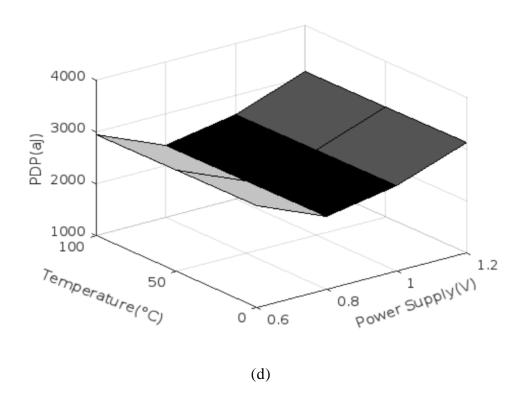

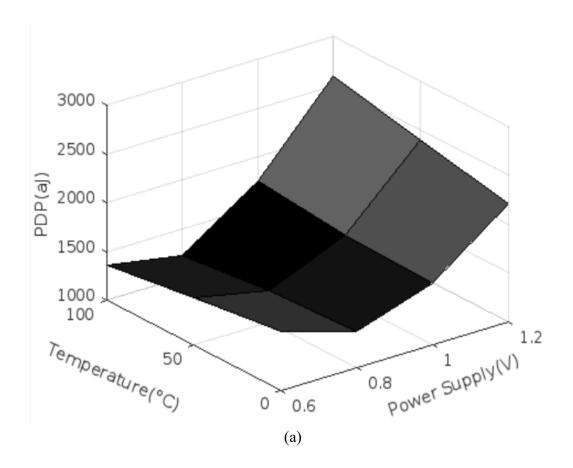

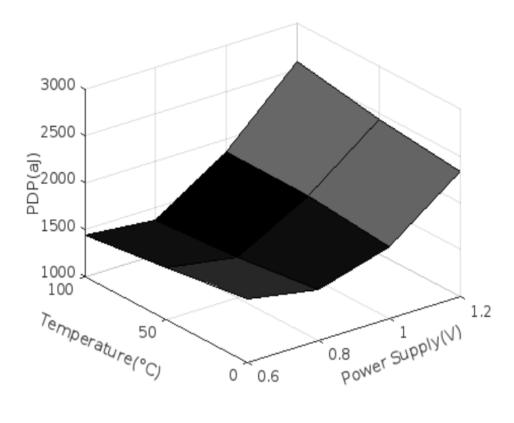

| Fig. 5.10 Effect of temperature and voltage variations on the PDP of 1-bit FA circuit at 32nm |

|-----------------------------------------------------------------------------------------------|

| (a) CMOS based footed DML design in static mode (b) CMOS based footed DML design in           |

| dynamic mode (c) Proposed C-DML design in static mode (d) Proposed C-DML design in            |

| dynamic mode                                                                                  |

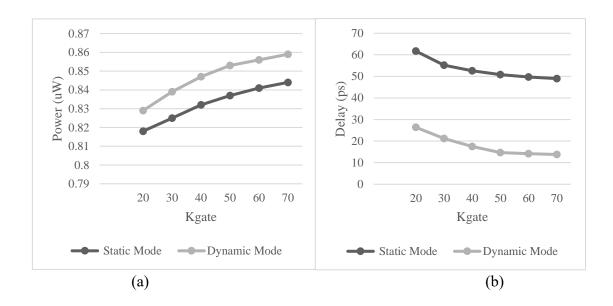

| Fig. 5.11 Effect of variation of dielectric constant (Kgate) for proposed type A C-DML based  |

| 2-input NAND gate in static and dynamic mode on (a) Power (b) Delay141                        |

| Fig. 5.12 Effect of variation of oxide thickness (Tox) for proposed type A C-DML based        |

| 2-input NAND gate in static and dynamic mode on (a) Power (b) Delay141                        |

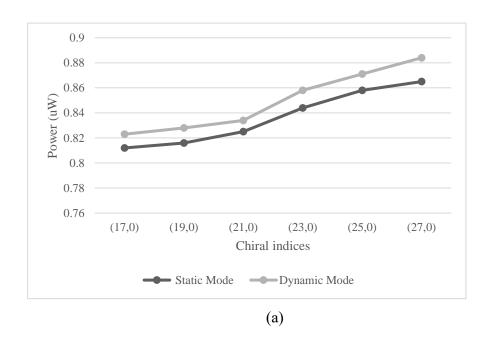

| Fig. 5.13 Effect of variation of chiral indices for proposed type A C-DML based 2-input       |

| NAND gate in static and dynamic mode on (a) Power (b) Delay142                                |

| Fig. 5.14 Proposed C-MDMTGDI cell                                                             |

| Fig. 5.15 Proposed C-MDMTGDI design (a) 2-input NAND gate (b) pre-charge phase of             |

| dynamic mode with no contention                                                               |

| Fig. 5.16 Transient waveforms of proposed C-MDMTGDI design for 2-input gates (a) Static       |

| mode (b) Dynamic mode                                                                         |

| Fig. 5.17 Transient waveforms of proposed C-MDMTGDI based 1-bit FA (a) Static mode (b)        |

| Dynamic mode                                                                                  |

| Fig. 5.18 C-DMTGDI cell                                                                       |

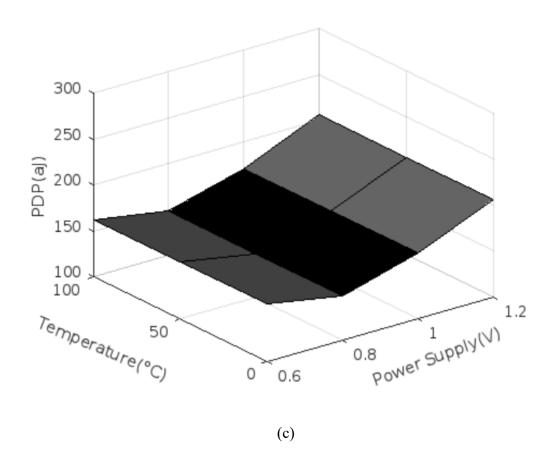

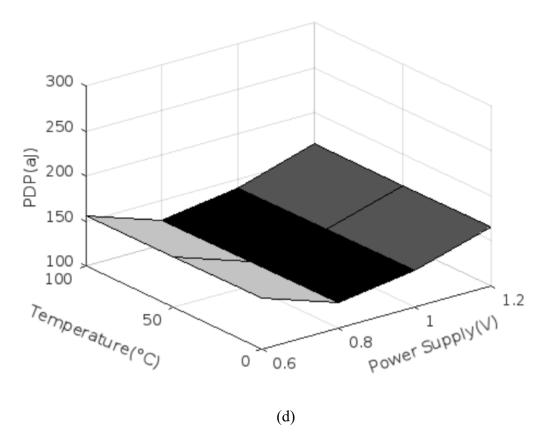

| Fig. 5.19 Effect of temperature and voltage variations on the PDP of 1-bit FA circuit at 32nm |

| (a) CMOS based M-DMTGDI design in static mode (b) CMOS based M-DMTGDI design                  |

| in dynamic mode (c) Proposed C-MDMTGDI design in static mode (d) Proposed                     |

| C-MDMTGDI design in dynamic mode                                                              |

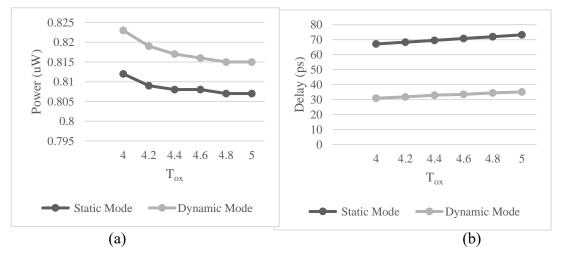

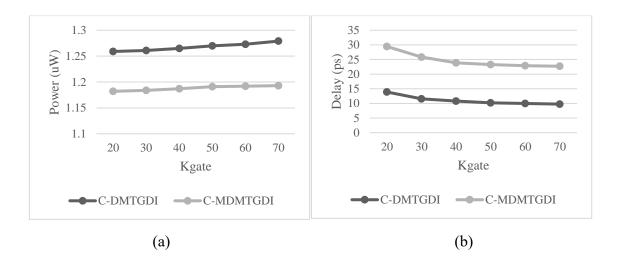

| Fig. 5.20 Effect of variation of dielectric constant (Kgate) for proposed C-MDMTGDI and       |

| C-DMTGDI based 2-input NAND gate in static mode on (a) Power (b) Delay155                     |

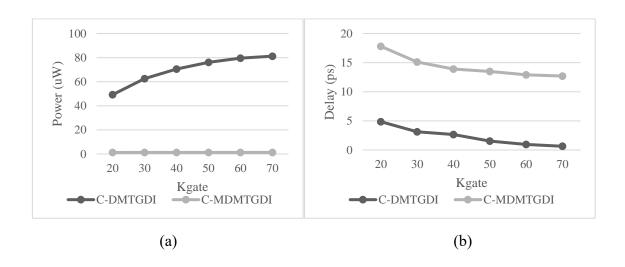

| Fig. 5.21 Effect of variation of dielectric constant (Kgate) for proposed C-MDMTGDI and  |

|------------------------------------------------------------------------------------------|

| C-DMTGDI based 2-input NAND gate in dynamic mode on (a) Power (b) Delay155               |

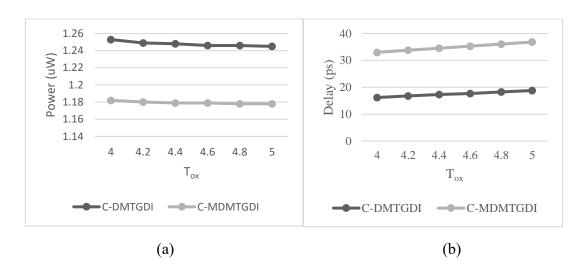

| Fig. 5.22 Effect of variation of oxide thickness (Tox) for proposed C-MDMTGDI and        |

| C-DMTGDI based 2-input NAND gate in static mode on (a) Power (b) Delay156                |

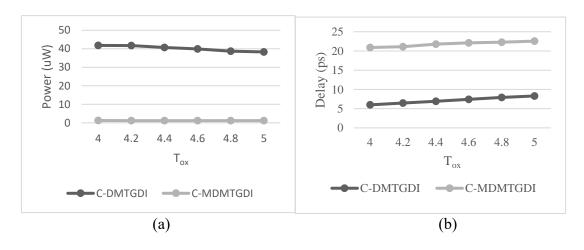

| Fig. 5.23 Effect of variation of oxide thickness (Tox) for proposed C-MDMTGDI and        |

| C-DMTGDI based 2-input NAND gate in dynamic mode on (a) Power (b) Delay156               |

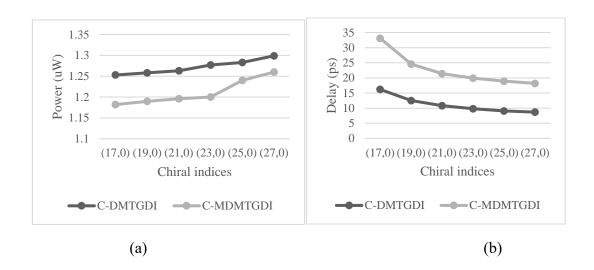

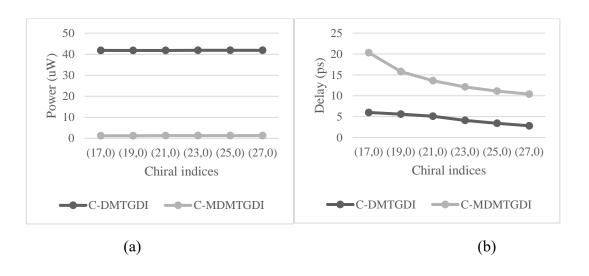

| Fig. 5.24 Effect of variation of chiral indices for proposed C-MDMTGDI and C-DMTGDI      |

| based 2-input NAND gate in static mode on (a) Power (b) Delay                            |

| Fig. 5.25 Effect of variation of chiral indices for proposed C-MDMTGDI and C-DMTGDI      |

| based 2-input NAND gate in dynamic mode on (a) Power (b) Delay157                        |

| Fig. 5.26 Proposed LECTOR based C-MDMTGDI 2-input NAND gate                              |

| Fig. 5.27 Proposed GALEOR based C-MDMTGDI 2-input NAND gate                              |

| Fig. 5.28 Proposed LCNT based C-MDMTGDI 2-input NAND gate                                |

| Fig. 5.29 Transient waveforms for LECTOR based C-MDMTGDI, GALEOR based                   |

| C-MDMTGDI and LCNT based C-MDMTGDI design of 2-input NAND gate at 32nm at                |

| 27°C in static mode                                                                      |

| Fig. 5.30 Transient waveforms for LECTOR based C-MDMTGDI, GALEOR based                   |

| C-MDMTGDI and LCNT based C-MDMTGDI design of 2-input NAND gate at 32nm at                |

| 27°C in dynamic mode                                                                     |

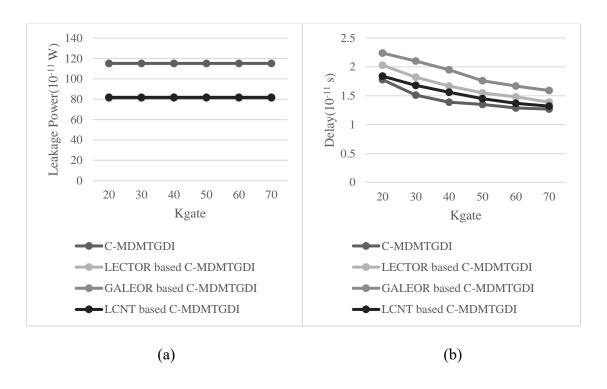

| Fig. 5.31 Effect of variation of dielectric constant (Kgate) for C-MDMTGDI, LECTOR based |

| C-MDMTGDI, GALEOR based C-MDMTGDI and LCNT based C-MDMTGDI for 2-input                   |

| NAND gate in static mode on (a) Leakage power (b) Delay                                  |

| Fig. 5.32 Effect of variation of dielectric constant (Kgate) for C-MDMTGDI, LECTOR based |

|------------------------------------------------------------------------------------------|

| C-MDMTGDI, GALEOR based C-MDMTGDI and LCNT based C-MDMTGDI for 2-input                   |

| NAND gate in dynamic mode on (a) Leakage power (b) Delay                                 |

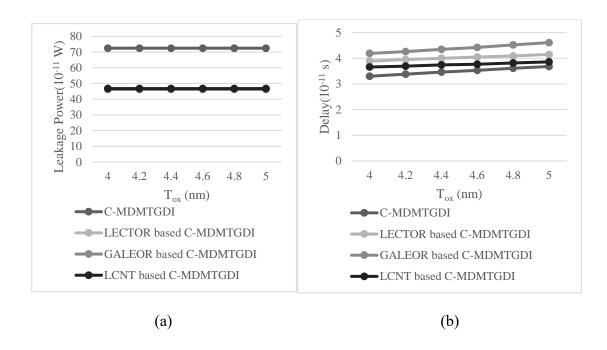

| Fig. 5.33 Effect of variation of oxide thickness (Tox) C-MDMTGDI, LECTOR based           |

| C-MDMTGDI, GALEOR based C-MDMTGDI and LCNT based C-MDMTGDI for 2-input                   |

| NAND gate in static mode on (a) Leakage power (b) Delay                                  |

| Fig. 5.34 Effect of variation of oxide thickness (Tox) C-MDMTGDI, LECTOR based           |

| C-MDMTGDI, GALEOR based C-MDMTGDI and LCNT based C-MDMTGDI for 2-input                   |

| NAND gate in dynamic mode on (a) Leakage power (b) Delay                                 |

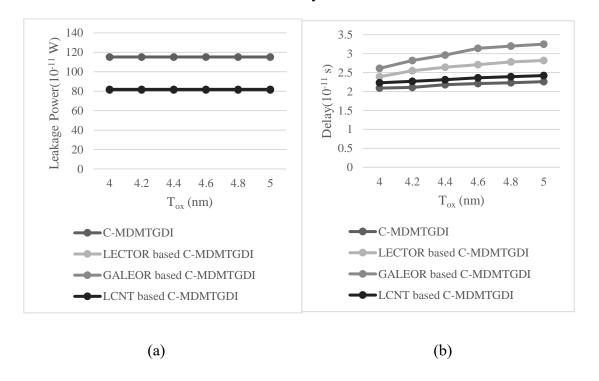

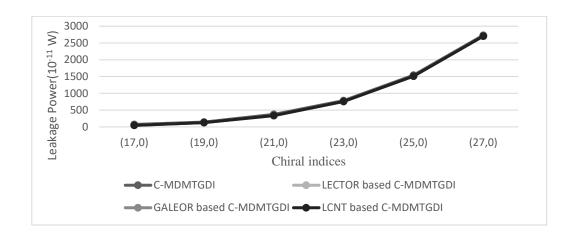

| Fig. 5.35 Effect of variation of chiral indices for C-MDMTGDI, LECTOR based              |

| C-MDMTGDI, GALEOR based C-MDMTGDI and LCNT based C-MDMTGDI for 2-input                   |

| NAND gate in static mode on (a) Leakage power (b) Delay                                  |

| Fig. 5.36 Effect of variation of chiral indices for C-MDMTGDI, LECTOR based              |

| C-MDMTGDI, GALEOR based C-MDMTGDI and LCNT based C-MDMTGDI for 2-input                   |

| NAND gate in dynamic mode on (a) Leakage power (b) Delay                                 |

### LIST OF TABLES

| Table 2.1 Summary of logic functions realized by DMTGDI cell [17]29                      |

|------------------------------------------------------------------------------------------|

| Table 3.1 Leakage power, delay and leakage PDP of proposed LDML and footed DML based     |

| 2-input type A and type B NAND and NOR gates and 1-bit FA circuit in static mode at 90nm |

| and 45nm at 27°C                                                                         |

| Table 3.2 Leakage power, delay and leakage PDP of proposed LDML and footed DML based     |

| 2-input type A and type B NAND and NOR gates, 1-bit FA circuit in dynamic mode at 90nm   |

| and 45nm at 27°C                                                                         |

| Table 3.3 Percentage leakage power saving for 2-input type A and type B NAND and NOR     |

| gates, 1-bit FA circuit in static mode for different temperature at 90nm                 |

| Table 3.4 Percentage leakage power saving for 2-input type A and type B NAND and NOR     |

| gates, 1-bit FA circuit in static mode for different temperature at 45nm                 |

| Table 3.5 Percentage leakage power saving for 2-input type A and type B NAND and NOR     |

| gates, 1-bit FA circuit in dynamic mode for different temperature at 90nm                |

| Table 3.6 Percentage leakage power saving for 2-input type A and type B NAND and NOR     |

| gates, 1-bit FA circuit in dynamic mode for different temperature at 45nm57              |

| Table 3.7 Leakage power, delay and leakage PDP of proposed GDML, GDMLD and footed        |

| DML based 2-input type A and type B NAND and NOR gates, 1-bit FA circuit in static mode  |

| at 90nm and 45nm at 27°C                                                                 |

| Table 3.8 Leakage power, delay and leakage PDP of proposed GDML, GDMLD and footed        |

| DML based 2-input type A NAND and NOR gates, 2-input type B NAND and NOR gates,          |

| 1-bit FA in dynamic mode at 90nm and 45nm at 27°C                                        |

| Table 3.9 Percentage leakage power saving for 2-input type A and type B NAND and NOR                 |

|------------------------------------------------------------------------------------------------------|

| gates, 1-bit FA in static mode for different temperature at 90nm                                     |

| Table 3.10 Percentage leakage power saving for 2-input type A and type B NAND and NOR                |

| gates, 1-bit FA circuit in static mode for different temperature at 45nm                             |

| Table 3.11 Percentage leakage power saving for 2-input type A and type B NAND and NOR                |

| gates, 1-bit FA circuit in dynamic mode for different temperature at 90nm79                          |

| Table 3.12 Percentage leakage power saving for 2-input type A and type B NAND and NOR                |

| gates, 1-bit FA circuit in dynamic mode for different temperature at 45nm80                          |

| Table 4.1 Region of operation of transistors T <sub>1</sub> , TN <sub>1</sub> and TP <sub>2</sub> 91 |

| Table 4.2 Power, delay and PDP of proposed M-DMTGDI, DMTGDI and footed DML based                     |

| 2-input NAND, NOR, XOR gates and 1-bit FA circuit in static and dynamic mode at 27°C                 |

|                                                                                                      |

| Table 4.3 Power, delay and PDP of proposed type A and type B DM-DCVSL in static mode                 |

| and static DCVSL for 2-input gates and 1-bit FA at 90nm at 27°C                                      |

| Table 4.4 Power, delay and PDP of proposed type A and type B DM-DCVSL in dynamic                     |

| mode and dynamic DCVSL for 2-input gates and 1-bit FA at 90nm at 27°C                                |

| Table 5.1 Power, delay and PDP of proposed type A and type B C-DML based and CMOS                    |

| footed DML based 2-input NAND, NOR, XOR gates and 1-bit FA circuit in static and                     |

| dynamic mode at 32nm at 27°C                                                                         |

| Table 5.2 Power, delay and PDP of existing CMOS based DMTGDI, CMOS based                             |

| M-DMTGDI, proposed C-DMTGDI and C-MDMTGDI based 2-input NAND, NOR, XOR                               |

| gates and 1-bit FA circuit in static and dynamic mode at 27°C                                        |

| Table 5.3 Leakage power and     | delay of C-MDMTGDI,       | LECTOR based     | C-MDMTGDI,  |

|---------------------------------|---------------------------|------------------|-------------|

| GALEOR based C-MDMTGD           | and LCNT based C-MDN      | MTGDI for 2-inpu | t NAND, NOR |

| and XOR gates in static and dyn | namic mode at 32nm at 27° | °C               | 165         |

## **Chapter 1**

# Introduction

### 1.1 Background

Nowadays, the low power designs of complex VLSI circuits are of utmost importance. With each technology generation, the integration density is increasing which is pushing power density and total power consumption to the limits that can be supported by packaging, cooling and other infrastructure [1]. Further, the rise in the demand of portable devices mainly cell phones and the proliferation of mobile applications and IoT solutions require efforts to curb power dissipation to have faster and durable devices with longer battery lifetime without compromising the performance [2]. Therefore, low power designs with improved performance i.e., energy efficient designs are considered essential [3].

Traditionally, static CMOS and dynamic domino designs have dominated the digital design arena for several decades with their respective limitations [4,5]. Large input capacitance and contention issues emerge with increased fan-in values and limits the usage of static CMOS for energy efficient designs [6]. Dynamic domino design offers less delay but at the cost of high energy, increased sensitivity to process variations, charge sharing and charge leakage problems [6,7]. The optimization of CMOS gate is quite challenging due to energy delay trade-off [7].

In order to have optimized designs in-terms of power and delay, efforts have been made to develop logic styles that can act as alternative to static CMOS. Some of the logic styles include Pass Transistor Logic (PTL) [8], Gate Diffusion Input (GDI) [9,10], Differential Cascode Voltage Switch Logic (DCVSL) [11-13], Dual Mode Logic (DML) [14-16], Dual Mode Transmission Gate Diffusion Input (DMTGDI) logic [17,18] and Dual Mode Pass Logic (DMPL) [19]. The PTL style [8] has the advantages of lesser transistor count and delay [8]. The GDI logic style [9] combines CMOS with PTL, and makes

implementation of logic functions simpler. The degradation of full swing at the output in PTL and GDI necessitates usage of additional buffers [9,10]. The DCVSL design provides output in both true and complemented forms. It is available in both static [11] and dynamic configurations [12]. Although the static DCVSL requires more power and is more sophisticated, it has the advantage of reducing parasitic capacitance. Another unique logic style, called DML, allows for flexible switching between static and dynamic operation modes [14]. The DML gates have great performance with marginally more power in the dynamic mode and very low power dissipation and moderate performance in the static mode [15]. As a result, energy efficient designs frequently employ this logic style [15-16]. The DML design has also been employed in conjunction with other logic styles- GDI and PTL in [17-19]. In DMTGDI, dual mode operation is made possible by an extra transistor (pre-charge/predischarge transistor) positioned between the output node and the supply voltage or ground [17]. Transmission Gate Diffusion Input (TGDI) logic is used to construct the logic in DMTGDI. This variation, like DML, utilises a mode signal to accommodate both static and dynamic operating modes [17]. In DMPL, a PTL network and an extra transistor are employed to realise a function with dual mode operation [19]. Using a mode signal, similar to DML, the DMPL-based designs can operate in static and dynamic mode [19].

The work has also been done to search for improved transistor technology that can lead to design with low power and high performance. Few of such technologies are-Fully Depleted Silicon On Insulator (FDSOI) [20-26], Fin Field-Effect Transistor (FinFET) [27-35], Carbon Nanotube Field-Effect Transistor (CNTFET) [36-48]. Recently, CNTFETs has gained popularity in digital domain mainly for low power designs. The CNTFET provides alternate channel material for transistors, which makes them faster and power efficient as

compared to bulk silicon transistors [36-40]. Presence of 1-D ballistic transport of charge carriers in CNTFETs has resulted in a high mobility and large drive current [39,40]. Also, these devices have large ON current (I<sub>on</sub>), higher I<sub>on</sub>/I<sub>off</sub> ratio and provide a unique property to control threshold voltage by simply changing the chiral indices or the diameter of the Carbon Nano Tube (CNT) [39,40].

### 1.2 Available Literature and Scope of Work

Substantial work has already been done by researchers in the quest for search of ways to reduce power in standard CMOS designs and at the same time, search for energy efficient logic styles and improved transistor technology based designs that can act as alternative to conventional CMOS designs. The existing literature can be classified into three main categories:

### 1.2.1 State of the art- Power reduction in standard CMOS designs

Power can be divided mainly into two types- static and dynamic power [1]. In generic terms, static power is the power consumed when the device is on but no signals are changing value while the dynamic power is consumed whenever the signal value changes [1].

In CMOS designs, the static power consumption is primarily due to leakage [3] whereas short circuit, glitching and switching power constitute dynamic power [3]. Till 180 nm technology node, dynamic power dominates the total power consumption [1]. However, at lower technology nodes, there is an increase in leakage power due to smaller feature size and threshold voltage reduction. As a result, leakage power surpasses dynamic power and becomes major contributor to total power of the design.

The short circuit power in CMOS designs is due to finite rise time and fall time of inputs, which makes both Pull Up Network (PUN) and Pull Down Network (PDN) simultaneously on. The finite propagation delay of gates may cause spurious transitions at the output and power dissipated in such an event is termed as glitching power [3]. Switching power is the power dissipated due to charging and discharging of capacitive loads. The switching power may be reduced by controlling physical capacitances, switching activity, clock frequency and supply voltage [3]. Some of the prevailing techniques to address these are clock gating [49-55], Multiple Supply Voltage (MSV) [56-65], Dynamic Voltage and Frequency Scaling (DVFS) [63-65] and Adaptive Voltage Scaling (AVS) [65-66].

The clock gating [49-55] minimises dynamic power by controlling the switching activity of the circuit. The basic idea behind the concept is to block the clock signal to the parts of circuit in which there is no change in value of output or to parts of circuit in which the stored value remains unchanged. To implement clock gating in a design, three cells have been used- gate based cell, latch-based cell, and flip flop-based cell [49-55]. The performance of these variants is compared in terms of power, area, and performance in [51]. It is inferred that for low power, gate-based cell is used while latch-based cell is suitable for high performance. Flip flop-based cell compromises both power and performance. In gate-based cell, glitching problem exists while latch-based cell suffers from sleep period i.e., a change in enable signal is not captured during this time which may lead to faulty design. Different types of flip flop [53-55] have also been designed using clock gating technique to reduce dynamic power.

The MSV technique [56-65] is yet another method used for dynamic power reduction in CMOS circuits. This technique involves supplying different parts of the circuit with

different voltages to reduce power while maintaining performance [56-58]. The dual supply technique at gate level is used in [57,58] by assigning low supply voltage to gates and flip flops lying on the critical path. There has been significant research in this area, including a new technique that combines critical/non-critical paths and switching activity analysis to assign different supply voltages [56]. In addition, energy efficient level converters have also been designed to overcome the delay and energy penalty associated with dual supply voltage designs [59-62]. A new low power level shifter is also presented for MSV designs in [60]. It uses multi-threshold CMOS technique and topological modifications to guarantee a wide voltage conversion range with limited penalty on static power and total energy consumption.

Another method of dynamic power reduction in CMOS is DVFS technique [63-65]. As dynamic power depends on voltage and frequency, so this dependence is used for DVFS technique [63,64]. Here, the voltage and frequency of the design are scaled dynamically for power reduction. It involves dynamically adjusting the supply voltage and clock frequency of a circuit based on its workload. Recent research has focused on developing novel DVFS techniques, such as per-core, per-chip, and cluster-level DVFS techniques [64], and AVS technique [65-66] to optimize power savings while maintaining performance. A separate voltage regulator is used for each core in per-core DVFS to have more control over power resulting in increased number of voltage regulators. This problem is resolved in per-chip DVFS by employing a single voltage regulator while compromising flexibility. So, to arrive at an intermediate solution, cluster level DVFS is proposed in [64]. In this technique, cores are grouped into multiple clusters depending on the workload and are driven by multiple regulators. The granularity of the design influences the efficiency and the cost of implementing DVFS. In AVS technique [65-66], voltage and frequency are dynamically

adjusted using a control loop. It achieves significant dynamic power reduction compared to open-loop voltage scaling techniques.

Another component which contributes significantly to total power is leakage power. In CMOS, it is caused by reverse bias diode leakage current, band-to-band tunnelling current, subthreshold leakage current, oxide tunnelling current hot carrier injection gate current, Gate Induced Drain Leakage (GIDL) current and channel punch through current [67]. Leakage power is now considered as the principal contributor to the total power consumption in many battery powered portable devices [67]. So, it necessitates the development of techniques to address leakage power issue. The first classification of leakage reduction techniques involves using different threshold voltage for transistors to minimize leakage [68-73]. Power gating is a technique that blocks current to unused parts of the circuit using sleep transistors [68]. Multi-threshold CMOS (MTCMOS) is another power gating technique that uses high threshold voltage transistors as sleep transistors to reduce leakage [68]. Dynamic Threshold MOSFET (DTMOS) involves varying the substrate bias with gate voltage to change the threshold voltage of a transistor dynamically [69-70], while Variable Threshold CMOS (VTCMOS) uses the concept of body effect to generate low and high threshold voltage for different transistors in the design [71]. The dual threshold technique assigns different threshold voltage to transistors based on the concept of critical and non-critical path [72]. VLSI CMOS LEAkage Reduction Technique (VCLEARIT) involves an additional circuit for sleep mode consisting of standard threshold voltage transistors and one high threshold voltage transistor to reduce leakage [73]. These techniques have certain drawbacks, such as additional sleep signal generation, increase in area and delay due to sleep transistors, and computational overhead of defining algorithms to decide the criticality of the paths involved.

Leakage reduction techniques can be further classified based on the concept of using stacking effect for leakage reduction [74-83]. Stacking effect states that leakage current reduces when the number of OFF transistors in the stack increases [74]. Techniques such as forced stack [74], sleepy stack [75], novel sleep technique [76], LEakage Control TransistOR (LECTOR) [77-79], GAted LEakage TransistOR (GALEOR) [80], GALEOR Stack [81], Leakage Control NMOS Transistor (LCNT) [82], Input-Controlled Leakage Restrainer Transistor (ICLRT) [83], Self-Control Leakage-Suppression Block (SCLSB) [84], Diode footed domino [85], LECTOR with footed diode [78], Lector based dual-Vt domino logic [79], Foot Driven Stack Transistor Domino Logic (FDSTDL) [86] and Domino Logic with Clock and Input Dependent Transistors (DOIND) [87] are based on this effect. Forced stacking technique uses two stacked transistors to reduce leakage current [74], while sleepy stack technique uses a high threshold voltage sleep transistor in parallel with the stacked transistors [75]. The novel sleep transistor technique connects a high threshold NMOS transistor in the PUN and a high threshold PMOS transistor in PDN [76]. The LECTOR technique inserts two Leakage Control Transistors (LCTs) between PUN and PDN to reduce leakage current [77], while GALEOR uses Gated Leakage Transistors (GLTs) [80]. Both the techniques use additional transistors to introduce stacking for leakage power reduction. However, both techniques suffer from limitations such as reduced output voltage swing, signal quality problems, and increased delay. The GALEOR Stack technique combines the GALEOR and forced stack technique, where half-size transistors are used along with high threshold GLTs between PUN and PDN [81]. This leads to a significant reduction in leakage power. The LCNT is another technique that uses two NMOS transistors between PUN and PDN [82]. It achieves better leakage power reduction with less delay penalty than LECTOR and GALEOR. However, it suffers from the disadvantage of having a low voltage level for logic low signals. ICLRT-based method attaches an input-controlled PMOS and an NMOS ICLRT to each path leading from either the supply voltage or the ground to the output. SCLSB inserts two PMOS and two NMOS transistors between PDN and PUN to increase resistance and decrease leakage current [83]. All these techniques reduce leakage power, but some have an area or delay penalty, and some require additional hardware for sleep signal generation.

Various techniques have also been proposed to reduce leakage power in domino circuits [78-79,86-87]. These include using the LECTOR technique with footed diodes [78] and multi-threshold domino [79], using FDSTDL with transistor stacking [86], and introducing DOIND transistors with controlled gate terminals to reduce leakage current [87]. These techniques involve additional transistors and may incur delay and area penalties, and some require specific input selection or additional hardware.

The third category of leakage reduction techniques includes hybrid designs and miscellaneous techniques [88-92]. These techniques combine multiple concepts to reduce leakage power. Examples include drain gating technique which uses stacking and sleep transistors [88], a hybrid design that combines Trimode MTCMOS power and ground gated techniques [89], and a novel technique that combines gate-level body biasing and DTMOS [90]. Other techniques include INput DEPendent (INDEP) [91], which uses input-dependent transistors, and ON/OFf LogIC (ONOFIC) [92], which provides a high-resistance path between supply and ground. These techniques offer reduced leakage power and improved performance but may also have limitations such as the need for extra control or computational overhead.

### 1.2.2 State of the art- Alternative Logic Styles

A wide range of alternative logic styles exist in literature- PTL [8,93,94], GDI [9,10,95-97], DML [14-16,98-105], DMTGDI [17,18], DMPL [19,100] and DCVSL[11-13]. The PTL uses pass transistor network to implement different logics with less transistor count and delay [8], while GDI combines CMOS and PTL logic styles and suffers from output voltage swing problem and low drive capability [9]. Various modifications have been proposed to overcome these issues, including using Conventional Complementary Metal-Oxide Semiconductor (CCMOS) based inverters [95] and adding additional transistors for level restoration [96]. These modifications improve the performance of GDI with reduced power consumption, corrected swing degradation, and increased performance.

The DML is yet another logic style [15,98] that offers two operational modes - static and dynamic - for power reduction and high performance, respectively. The DML can be implemented using two topologies, type A and type B, and various techniques have been proposed for DML to minimize power consumption and area [99-105]. Mixed mode of operation [99,101], which combines static and dynamic modes, has been exploited for energy efficiency in DML-based carry save adders and multipliers [99]. Leakage reduction techniques, such as the self-controllable voltage level logic [100], have also been employed to reduce power in both static and dynamic modes. Additional controllers have been added to identify parts of the circuit to be operated in low power static mode and high-speed dynamic mode, which is referred to as mixed mode of operation [100]. Further a self-adaptive mechanism is used with DML logic style to operate the circuit in mixed DML mode [101]. A DML-based comparator has also been presented in [103] with high speed and low power

consumption by limiting the switching operations of internal nodes. However, some of these techniques have led to an increase in area overhead due to the presence of additional circuitry.

In addition to these, novel DML based logic styles are proposed which aims at exploiting DML benefits with minimum area or number of transistors. Two such logic styles are DMPL [19,102] and DMTGDI logic [17,18]. The DMPL design combines energy efficiency of PTL in static mode with high performance of DML design in dynamic mode [19]. A standard DMPL gate replaces the minimum size network of a DML design with a minimum-sized PTL-based network [19]. In [17], a modification to GDI logic, referred to as Transmission Gate Diffusion Input (TGDI), is introduced. Additional transistors are used in TGDI to provide dual mode operation and the design so arrived is called DMTGDI [17]. Various logic functions can be implemented with a few transistors using this logic style [17]. Both DMPL and DMTGDI configurations suffer from contention issue in dynamic mode of operation, so transistor sizing is critical to maintain proper voltage level at the output.

The DCVSL is another logic style that has been shown to be energy efficient and can exist in static [11] and dynamic (clocked) [12] configuration while providing output in true and complemented forms. This logic style utilizes NMOS logic trees to implement logic, which contributes to its high performance. While static DCVSL provides the advantage of reduced parasitic capacitance, it comes with increased power and complexity [11]. To improve performance, dynamic DCVSL designs have also been examined [12]. Leakage control technique has also been employed in both the static and dynamic configurations of DCVSL [11]. It involves the use of leakage control transistors and multi-threshold logic to achieve leakage reduction [11].

#### 1.2.3 State of the art- Improved Transistor Technology

Research has also been done to search improved transistor technology with low power, high performance, and better control of device parameters. Improved transistor technology devices have allowed for successful implementation of many logic styles previously used in CMOS. Few of the technologies are- FDSOI [20-25,104,105], FinFET [27-35,106-110], CNTFET [36-48,111-118].

The FDSOI is an emerging technology that has several benefits compared to bulk silicon, such as a simplified manufacturing process and improved transistor performance [20-23]. By adding a thin layer of insulator beneath the channel, switching power is reduced, and channel control is improved. The Ultra-Thin Body and Buried Oxide FDSOI (UTBB FDSOI) utilizes an extremely thin transistor body that allows it to operate at lower voltage and with higher performance than conventional transistors [24,26]. The DML logic style, discussed earlier, has been successfully implemented using UTBB FDSOI technology, enabling the design of high energy efficient digital systems [99].

The FinFET, on the other hand, is another transistor technology, which can act as an alternative to CMOS as the devices are moving to lower technology node, allowing scaling of devices beyond 20nm [27-35,106-110]. Many of the logic styles- PTL, GDI, Transmission Gate Logic (TGL), Complementary Pass Transistor Logic (CPL)-which existed in CMOS domain, have been successfully implemented using FinFETs [106-110] and it was found that these logic styles achieve significant PDP reduction in FinFET domain. Studies have also been carried out to reduce leakage in FinFETs [27-35]. Several leakage reduction techniques such as ONOFIC [27,34], LECTOR [34], Drain Gating [35], LCNT [109] and INDEP [110], which were originally developed for CMOS, have been implemented using FinFETs. The

results have shown that these techniques effectively reduce leakage power in FinFETs. Some of the new techniques i.e., Leakage Controlling Pass Transistor (LCPT), Self-Controllable Voltage Level (SVL) are also introduced for FinFETs. In [106], a variant of LECTOR and LCNT leakage reduction technique is proposed which incorporates N-type and P-type LCPTs to introduce stacking which reduces leakage. Further, LCTs are added as sleep transistors for enhanced leakage reduction. Another novel approach introduced in [107] is Self-Controllable Voltage Level (SVL) technique and involves the use of three different types of SCVL circuits - Upper (USVL), Lower (LSVL), and Type 3 (a combination of the upper and lower SVL circuit designs). The SVL technique is designed to reduce leakage power by controlling the voltage levels during the standby mode.

Another device which has gained popularity in digital domain mainly for low power designs is CNTFET [36-48,111-118]. Various MOSFET based logic styles, which are already discussed, have successfully been implemented in CNTFET domain and it is found that these CNTFET based logic styles- C-CMOS, CPL, domino, TG-CNTFET, GDI- exhibit better PDP as compared to conventional MOS [39]. The GDI logic style is popular in the CNTFET domain due to its excellent performance in terms of power, delay, and PDP, but it has a drawback of reduced output voltage swing [111-113]. To address this issue, a Modified GDI (MGDI) logic style has been proposed [112]. When combined with CNTFETs, the MGDI logic style produces smaller, faster, and higher performance devices compared to CMOS designs [112]. TGDI logic style is also utilized in the CNTFET domain, and offers improvements in power, delay, and PDP over traditional GDI [114].

In addition, these devices provide a unique opportunity to control threshold voltage by changing the chiral indices or the diameter of CNT. As a result, these devices are widely used for multi-valued logic implementation also, proposed in [46-47]. Another area of research that has emerged in CNTFET domain is leakage power. Limited study has been conducted on the implementation of techniques for reducing leakage in CNTFETs, using the methods previously developed for MOSFETs [115-121]. In [115], the efficiency of two methods is assessed for lowering CNTFET subthreshold leakage. For leakage reduction, a negative bias is applied to the n-type CNTFET's gate in the first method, and pull-down networks are stacked in CNTFET-based designs, referred to as stack forcing in the second method. In [116], leakage reduction techniques- sleep transistor, forced stack, data-retention sleep transistor and stacked sleep have been investigated in CNTFET domain. It is found that these techniques are adept at reducing leakage even in CNTFET domain. However, they impose an area penalty. Some novel techniques have also been proposed for leakage reduction in CNTFETs [119-121]. One such technique is proposed in [119-120] which uses the concept of dual chiral indices (multi-VTH) to reduce leakage in CNTFETs. Another method, presented in [121], reduces subthreshold leakage current and improves the noise margin by introducing a feedback structure that controls the transistor's threshold voltage. Although many methods have been developed to address leakage in CNTFETs, research in this area remains limited. Therefore, there is a need to investigate additional strategies for reducing leakage in the context of CNTFETs.

### 1.3 Research Gaps

As the technology is scaled down to deep nanometre regime, power mainly leakage power, in CMOS based designs is increasing at an exponential rate. Many techniques have already been proposed to tackle this issue, but these techniques have some limitations associated with them, as already discussed. Another point to be noted is that in deep

nanometre regime, dynamic power is no more a dominant component of power in CMOS devices. Even after extensive research, the issue of increased power still persists especially when technology node is continuously scaled down. So, there is a need to search for transistor technology and logic styles, which can act as a substitute to CMOS so as to have power efficient designs. These emerging logic styles and technology inherently offer the advantage of low power along with other merits as compared to CMOS. Power reduction techniques are also required for these alternative logic styles to have low power designs. Further the improved transistor technology mainly FinFET, CNTFET and alternative logic styles can be explored and further power reduction is possible in the designs based on these. These new technologies offer great opportunity for low power designs with enhanced performance. So, the research gaps can be summarized as:

- ➤ There is a need for search of alternative logic styles and improved transistor technologies that can act as low power alternatives to CMOS.

- ➤ Power reduction techniques-specially targeting leakage power-need to be explored for alternative logic styles.

- ➤ For improved transistor technologies, the power reduction strategies can further be explored for low power designs.

#### 1.4 Research Objectives

Based on the literature review and the research gaps identified thereafter, the following objectives are set for the research work:

- > To develop techniques for leakage power reduction in alternative logic styles.

- > To formulate techniques that mitigate total power in alternative logic styles

- ➤ Development of leakage power reduction techniques in circuits based on improved transistor technology.

- To investigate total power reduction methods in improved transistor technology-based circuit designs.

In order to achieve the objectives, the following are the highlights of the work carried out:

- i. Two designs are proposed for leakage power reduction in footed DML circuits referred to as GALEOR with Dual Mode Logic (GDML) and GALEOR with Dual Mode Logic with footed Diode (GDMLD). Also, LECTOR technique is proposed for footed DML circuits referred to as LDML, which leads to significant leakage power reduction in footed DML circuits.

- ii. A modification of DMTGDI logic style, referred to as Modified DMTGDI (M-DMTGDI) design, is presented which provides PDP reduction and resolves the contention issue in existing DMTGDI design. Also, a modification to existing static DCVSL design is proposed and is referred to as Dual Mode DCVSL (DM-DCVSL) design. The proposed design provides both power saving and delay reduction.

- iii. CNTFET based Modified DMTGDI design and CNTFET based DMTGDI design, referred to as C-MDMTGDI design and C-DMTGDI design, respectively are proposed which offer PDP reduction. The proposed C-MDMTGDI design overcomes the contention issue in C-DMTGDI design. Further leakage reduction techniques-LECTOR, GALEOR and LCNT are proposed for C-MDMTGDI design.

- iv. CNTFET based DML (C-DML) design is proposed which offers PDP reduction in both static and dynamic mode.

#### 1.5 Organization of the thesis

Following is the brief description of chapters:

#### Chapter 1:

This chapter gives a background and literature review of power reduction in standard CMOS designs, alternative logic styles and improved transistor technologies. It further states the objectives set for exploring novel alternative logic styles and their power reduction.

#### Chapter 2:

This chapter presents an elaborative description of various alternative logic styles-DML, DMTGDI and DCVSL. For each alternative logic style, the operation and analysis of 2-input NAND gate is discussed.

#### Chapter 3:

This chapter discusses three novel leakage reduction techniques for footed DML design- LDML, GDML, and GDMLD. Firstly, the operation of the proposed designs is elaborated and then the simulative investigation of circuits based on proposed designs is done with functional verification and performance comparison.

#### Chapter 4:

This chapter is devoted to two proposed DML based designs- M-DMTGDI and DM-DCVSL. First existing DMTGDI and DCVSL designs are discussed and then the proposed designs are put forward with their operation and simulation results. Each of the proposed design based circuit is functionally verified and then a performance comparison is done.

#### Chapter 5:

This chapter elaborates the implementation of footed DML and M-DMTGDI design in CNTFET domain. Further, leakage reduction techniques-LECTOR, GALEOR and LCNT are also proposed for C-MDMTGDI design. Extensive simulation of the proposed designs is done to check the proposed design's functionality and a performance comparison is drawn between the existing and proposed design.

#### Chapter 6:

This chapter summarizes the work presented in the thesis and the future scope of the work.

All throughout the thesis, the simulations for functional verification and performance comparison for MOSFET based designs are performed using Symica DE tool and for CNTFET based designs, HSPICE tool is used.

## Chapter 2

# **Alternative Logic Styles: Basic Concepts**

#### 2.1 Introduction

This chapter provides an overview of various alternative logic styles, delving into their fundamentals and operational aspects. The alternative logic styles covered in this chapter include DML, DMTGDI and DCVSL.

#### 2.2 Dual Mode Logic (DML)

The DML is an alternative logic style which allows two operational modes in a design i.e., static and dynamic mode [14-16]. This logic family has two variants-unfooted and footed [14]. Further, two topologies i.e., type A and type B exist in each of these variants. The DML fundamentals and operation of DML 2-input NAND gate are discussed in the following subsections.

#### 2.2.1 DML fundamentals

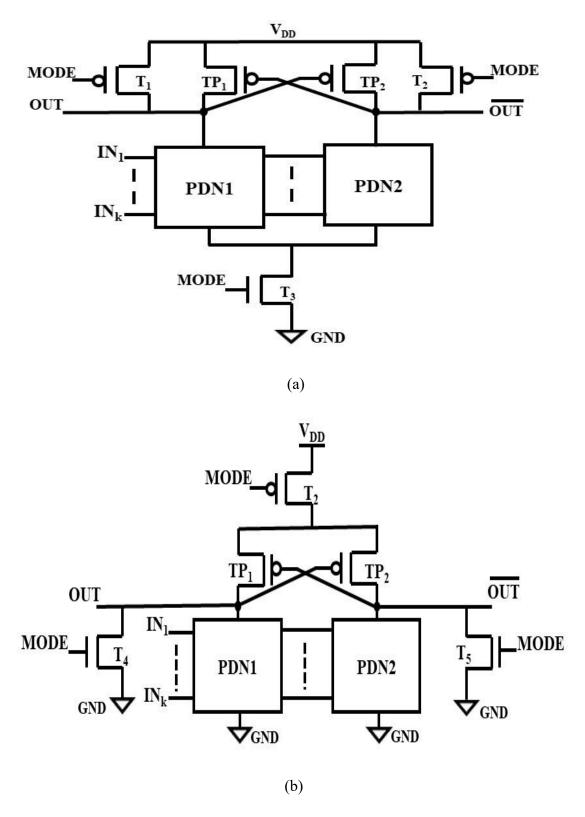

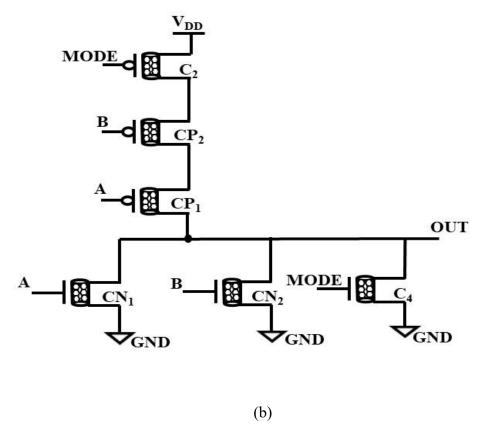

The unfooted DML design consists of PUN and PDN with an extra pre-charge/pre-discharge transistor [15]. It can be implemented via two topologies- type A and type B as shown in Fig. 2.1. A pre-charge transistor (T<sub>1</sub>) and pre-discharge transistor (T<sub>4</sub>) is added at the output of a conventional CMOS gate for type A and type B topology respectively. In static mode, the MODE input is at logic "1" (logic "0") for type A (type B) which makes transistor T<sub>1</sub> (T<sub>4</sub>) off . For dynamic mode, a clock signal is used as MODE input which permits two phases of operation-pre-charge (pre-discharge) and evaluation for type A (type B). The output node is charged to supply voltage (discharged to ground (GND)) using T<sub>1</sub> (T<sub>4</sub>) transistor in type A (type B) topology in pre-charge (pre-discharge) phase as MODE input is logic "0" (logic "1"). In evaluation phase of dynamic mode, the MODE input is logic "1" (logic "0"),

as a result, transistor  $T_1$  ( $T_4$ ) becomes off. The applied inputs decide the state of output in both type A and type B designs.

Fig. 2.1 DML design (a) Unfooted type A [14] (b) Unfooted type B [14]

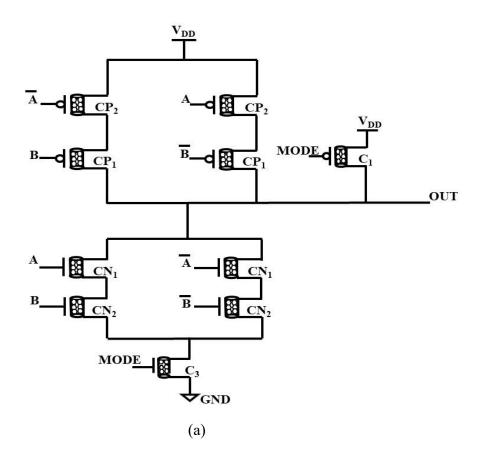

Basic structure of a footed DML gate is given in Fig. 2.2. The type A footed design consists of an additional NMOS transistor (T<sub>3</sub>), placed between PDN and ground along with pre-charge transistor (T<sub>1</sub>), as shown in Fig. 2.2 (a). Similarly, for type B, this design includes an additional PMOS transistor (T<sub>2</sub>) between PUN and supply voltage along with pre-discharge transistor (T<sub>4</sub>), as shown in Fig. 2.2 (b). In static mode, the MODE input is at logic '1" for type A and logic "0" for type B topology [14]. The additional footer transistor (T<sub>3</sub>) is turned on in type A. In type B topology, the header transistor (T<sub>2</sub>) is turned on. For dynamic mode, a clock signal is used as MODE input which permits two phases of operation-pre-charge (pre-discharge) and evaluation for type A (type B).

For type A footed DML design, the output node is charged to  $V_{DD}$  using  $T_1$  transistor in pre-charge phase. At this time, the footer transistor  $(T_3)$  remains off. Analogously, the

output node is discharged to ground using T<sub>4</sub> transistor in type B footed DML topology in pre-discharge phase. The header transistor (T<sub>2</sub>) remains off.

In evaluation phase, transistor  $T_1$  is off for type A topology. At the same time, the additional footer transistor  $(T_3)$  is turned on. In type B topology, transistor  $T_4$  is off and the header transistor  $(T_2)$  is on. As a result, the applied inputs decide the output in both type A and type B designs in evaluation phase.

Fig. 2.2 DML design (a) Footed type A [14] (b) Footed type B [14]

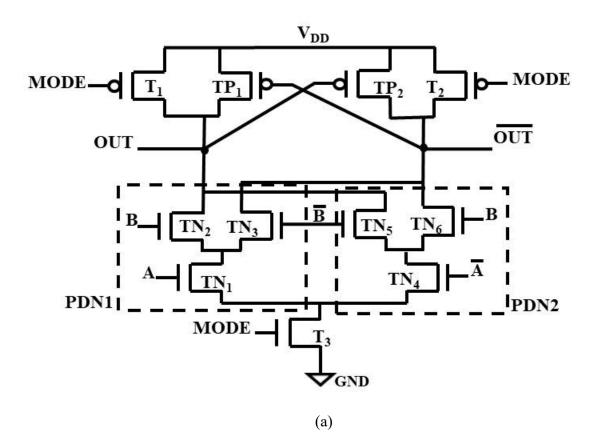

#### 2.2.2 Operation of DML 2-input NAND gate

To understand the operation of both unfooted and footed DML design, a 2-input NAND gate is considered, as shown in Fig. 2.3 and Fig. 2.4. The operation of an unfooted DML based 2-input type A NAND gate is described next. In static mode, the MODE input is at logic "1" so the pre-charge transistor  $(T_1)$  remains off. The output is calculated according to the inputs applied. When (A, B) = (1, 1), both NMOS transistors  $TN_1, TN_2$  are on, and

PMOS transistors  $TP_1$ ,  $TP_2$  are off. A direct path is created between output node and ground, resulting in logic "0" at the output. When the input (A, B) = (0, 0), both NMOS transistors  $TN_1$ ,  $TN_2$  are off and simultaneously, PMOS transistors  $TP_1$ ,  $TP_2$  are on. As a result, a path is created between output node and  $V_{DD}$ , causing a logic "1" at the output node. Similarly, in the case of (A, B) = (0, 1), the  $TP_1$  and  $TN_2$  transistors are on, while  $TN_1$  and  $TP_2$  transistors are off. Consequently, a connection forms between the output node and  $V_{DD}$ , leading to a logic "1" output. When (A, B) = (1, 0), the  $TP_1$  and  $TN_2$  transistors are off, while  $TN_1$  and  $TP_2$  transistors are on, thus creating a path between output node and  $V_{DD}$  resulting in logic "1" output. Thus, the circuit realizes NAND function.

For dynamic mode, the MODE input is supplied with a clock signal having two phases of operation- pre-charge and evaluation. In pre-charge phase, as MODE input is logic "0", transistor  $T_1$  is on. Therefore, the output is charged to  $V_{DD}$ . In evaluation phase, MODE input is logic "1" so the pre-charge transistor  $(T_1)$  remains off. For inputs (A, B) = (1, 1), NMOS transistors  $TN_1$ ,  $TN_2$  are on, and PMOS transistors  $TP_1$ ,  $TP_2$  are off, causing a path to be created between output and ground. As a result, the output attains logic "0" value. When (A, B) = (0, 0), NMOS transistors  $TN_1$ ,  $TN_2$  are off, and PMOS transistors  $TP_1$ ,  $TP_2$  are on, thus creating a path between output and  $V_{DD}$ , which yields a logic "1" output. Similarly, with (A, B) = (0, 1),  $TP_1$  and  $TN_2$  transistors are on, while  $TN_1$  and  $TP_2$  transistors are off, creating output to  $V_{DD}$  path to make output as logic "1". Lastly, for (A, B) = (1, 0),  $TP_1$  and  $TN_2$  transistors are off, while  $TN_1$  and  $TP_2$  transistors are on. This establishes a connection between the output and  $V_{DD}$ , resulting in a logic "1" output.

Similar analysis can be done for unfooted DML based 2-input type B NAND gate in static and dynamic mode, as depicted in Fig. 2.3 (b). In static mode, the pre-discharge transistor (T<sub>4</sub>) is off and the output is evaluated according to applied inputs. In pre-discharge phase of dynamic mode, pre-discharge transistor (T<sub>4</sub>) is on and it discharges the output node to ground. In evaluation phase, the output is evaluated according to applied inputs, as the pre-discharge transistor (T<sub>4</sub>) is off.

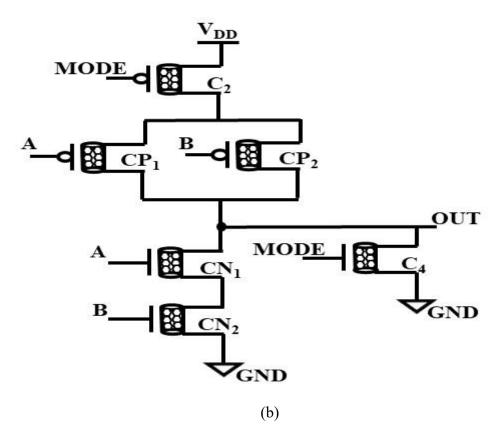

Fig. 2.3 DML based 2-input NAND gate (a) Unfooted type A (b) Unfooted type B Consider a footed DML based 2-input type A NAND gate, shown in Fig. 2.4 (a). In static mode, the operation is same as that of an unfooted DML based 2-input type A NAND gate with the pre-charge transistor T<sub>1</sub> as off and the footer transistor T<sub>3</sub> as on. For dynamic mode, the MODE input is supplied with a clock signal having two phases of operation-pre-charge and evaluation. In pre-charge phase, as MODE is logic "0", transistor T<sub>1</sub> is on,

footer transistor  $T_3$  is off. Therefore, the output is charged to  $V_{DD}$ . In evaluation phase, the pre-charge transistor  $T_1$  remains in the off state, while the footer transistor  $T_3$  is turned on. The operation is same as that of an unfooted DML based 2-input type A NAND gate in evaluation phase.

Similar analysis can be done for footed DML based 2-input type B NAND gate in static and dynamic mode, as depicted in Fig. 2.4 (b). In static mode, the pre-discharge transistor  $(T_4)$  remains off, while the header transistor  $(T_2)$  is on, allowing the output to be assessed based on the inputs applied. In the pre-charge phase of dynamic operation, the header transistor  $(T_2)$  is off, and the pre-discharge transistor  $(T_4)$  is on to discharge the output node to ground. During the evaluation phase, the output is determined based on the applied inputs, with the pre-discharge transistor  $(T_4)$  turned off and the header transistor  $(T_2)$  as on.

Fig. 2.4 DML based 2-input NAND gate (a) Footed type A (b) Footed type B

In unfooted DML design, specific input combinations can potentially lead to contention during the pre-charge phase because a path exists between the supply voltage and ground. Consequently, appropriate transistor sizing becomes necessary to guarantee a complete voltage swing at the output. To elucidate this, consider an unfooted DML based 2-input type A NAND gate in pre-charge phase with both inputs (A, B) = (1,1). In pre-charge phase, MODE is at logic "0" and the transistor T<sub>1</sub> starts charging the output node, OUT to V<sub>DD</sub>. The PDN of NAND gate is on and it starts discharging the output node. Therefore, proper output voltage is not obtained in that case. Similarly, contention occurs in unfooted DML based 2-input type B NAND gate between the pre-discharge transistor (T<sub>4</sub>) and PUN in pre-discharge phase when both inputs (A, B) = (0,0). This issue is resolved in footed DML gates due to the presence of footer and header transistor in type A and type B topology respectively. In a type A design, the discharging of the output is prevented by the off footer transistor (T<sub>3</sub>) during the pre-charge phase. Similarly, in a type B design, the charging of the output node is prevented by the on header transistor (T<sub>2</sub>) during the pre-discharge phase. Therefore, full output voltage swing is achieved. Additionally, the unfooted DML gates exhibit short-circuit power issues during the pre-charge phase, an extended pre-charge duration, increased sensitivity to process variation, and reduced overall robustness [15].

#### 2.3 Dual Mode Transmission Gate Diffusion Input (DMTGDI)

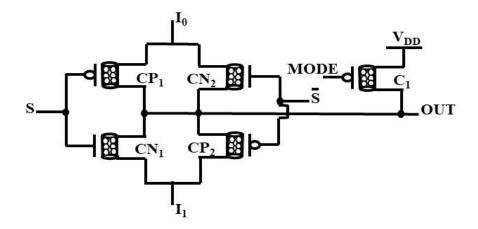

The DMTGDI design introduces dual mode capability in TGDI design by incorporating an additional transistor (pre-charge/pre-discharge transistor) between the output node and the supply voltage/ground [17]. Similar to DML, this variant also supports both static and dynamic operating modes which can be selected using a mode signal [17-18].

It can exist in two topologies- type A and type B. The DMTGDI fundamentals and operation of DMTGDI 2-input NAND gate are discussed in the following subsections.

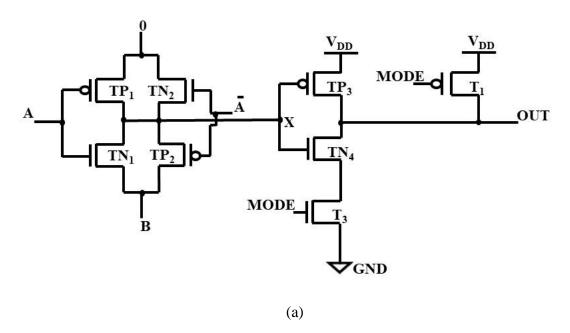

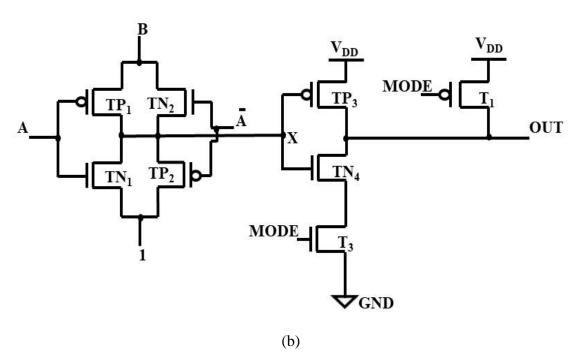

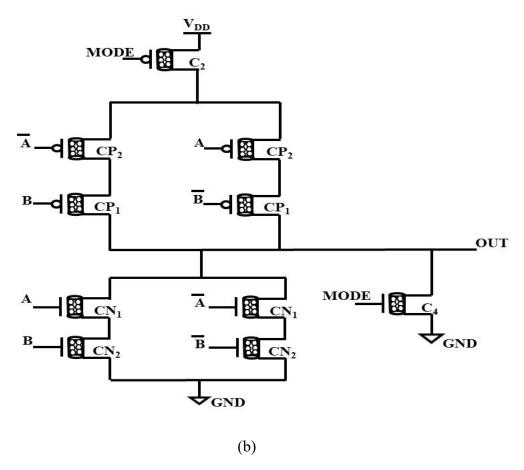

#### 2.3.1 DMTGDI fundamentals